## Design and Implementation of Trim-free Voltage and Current References for Energy-Efficient IoT Applications

Thesis submitted in partial fulfilment of the requirements for the degree of

Master of Science in Electronics and Communication Engineering by Research

# Chetan Mittal 2021702019

chetan.mittal@research.iiit.ac.in

International Institute of Information Technology Hyderabad - 500 032, INDIA June 2024 Copyright © Chetan Mittal, June 2024. All Rights Reserved

## International Institute of Information Technology Hyderabad, India

## CERTIFICATE

It is certified that the work contained in this thesis, titled "Design and Implementation of Trim-free Voltage and Current References for Energy-Efficient IoT Applications" by Chetan Mittal, has been carried out under my supervision and is not submitted elsewhere for a degree.

Date

Advisor: Dr. Zia Abbas

To the Past, Present and Future

### Acknowledgments

I begin this acknowledgment by expressing my sincere thanks to Professor Dr. Zia Abbas. He has been more than just an advisor to me during my time at IIIT-Hyderabad; he has been a mentor and a close guide. His unwavering support and guidance have been crucial to my academic journey. Dr. Abbas's unique approach to encouraging innovation and his focus on teamwork have been a great source of motivation for me, pushing me to strive for excellence in research. Additionally, he has taught me the importance of being passionate about my work and showing kindness to others, which have not only shaped my academic growth but also my personal development.

My initial interest in Analog Circuit design was sparked by online resources like NPTEL lectures, which I found to be highly intuitive and easy to understand. These lectures were delivered by renowned experts in the field, including Dr. Shanthi Pavan from IIT-Madras, Dr. Nagendra Krishnapura from IIT-Madras, Dr. Behzad Razavi from UCLA, Dr. Ali Hajimiri from CalTech. These resources not only helped me grasp the fundamentals of Analog Circuit design but also inspired me to delve deeper into the field. The clarity and depth of the lectures provided me with a solid foundation, motivating me to pursue further study and research in this area. I thank Intel semiconductors for introducing me to the real fabrication issues from industry perspective. I would like to express my gratitude to Micron Technology for providing me with an opportunity to gain a better understanding of circuit design.

I would like to express my thank to my seniors namely Ashfakh Ali, Arpan jain, Abhishek pullela, Arnab Dey, Samriddhi agarwal, Koushik De, Deepthi Amuru for their constant guidance and countless discussions which helped me to find insights on various topics of my research projects. My colleagues Bhartipudi sahishnavi, Anubhab Banerjee, Subramaniam Bharadwaj and Dheekshith Akula, with whom I had my initial discussions over a wide range of topics and my juniors Shiva and Mehul which help me to gain different perspective of any project.

My experience at IIIT Hyderabad would not have been complete without the support of my dearest friends Arpit sahni, Srayan Sankar Chatterjee and Ashish papreja, whose unwavering support and encouragement have been instrumental in my journey.

Finally, I express my deepest gratitude to my parents, whose wisdom has been a guiding light throughout my education. They have stood by me in difficult times, shaping my character with values of integrity, perseverance, and gratitude. Their unwavering support has been the foundation of my academic journey, and I am forever grateful for their love and guidance.

### Abstract

The Internet of Things (IoT) has witnessed exponential growth, enabling a plethora of smart applications ranging from wearable devices to smart cities. However, the widespread adoption of IoT devices hinges on their ability to operate with minimal power consumption. However, one of the critical challenges in IoT design is the need for ultra-low power consumption to enable long battery life and energy harvesting. Moreover, systems powered by energy harvesting sources need to operate effectively with lower supply voltages. Similarly, systems relying on miniaturized batteries must be capable of functioning over a broad range of supply voltages, eliminating the necessity for voltage regulators.

Low power, high precision and low supply voltages are the primary requirement of an IoT based design. Voltage and current references are the basic blocks used in IoT based system. This thesis focuses on the designing of Voltage and current references circuit with low power consumption, low supply voltage and high precession without using any external calibration circuit.

Firstly. the thesis introduces a All-in-one low-power, voltage and current reference design into a single block without using any external calibration. The design works with a supply of 1V with a power consumption of 37nW shows temeprature invariancy through a wide tempertaure range of -40 to 100°C. This design specification shows the best results among the previous state-of-art works. Furthermore, in response to the growing demand of low power high precsion circuits we designed an ultra-low power current reference circuit which is independent of temperature, voltage and process without using any extra trimming circuitry. The design works with a supply of 0.8V and generates a refrence current of 543pA by consuming a power of 3.3nW. Lastly, we come up with a novel design of voltage reference. The proposed work is designed in 180nm with a supply voltage of 0.6V with an excellent Line sensitivity of 0.0012/V without using an external calibration circuit.

In summary, this thesis encompases the circuit designing of low power, low voltgae and high accuracy voltage and current references without using resistors, amplifiers and external calibration circuit used in IoT applications.

## Contents

| Ch | napter              | I                                                                                        | Page        |

|----|---------------------|------------------------------------------------------------------------------------------|-------------|

| 1  | Intro<br>1.1<br>1.2 | duction                                                                                  | 1<br>2<br>3 |

| 2  | Liter               | ature Review                                                                             | 5           |

|    | 2.1                 | Introduction                                                                             | 5           |

|    | 2.2                 | Subthreshold region(Weak inversion region) of MOSFETs                                    | 5           |

|    | 2.3                 | Process, voltage and temperature independent Analog circuits                             | 6           |

|    |                     | 2.3.1 Temperature variation                                                              | 7           |

|    |                     | 2.3.2 Voltage variation                                                                  | 7           |

|    |                     | 2.3.3 Process Variation                                                                  | 8           |

|    |                     | 2.3.4 Fundamental Analog blocks : Voltage and current reference                          | 9           |

|    |                     | 2.3.4.1 Generation of Voltage and current reference                                      | 9           |

|    |                     | 2.3.5 Methods of generating PTAT and CTAT voltage/current                                | 11          |

| 3  | A 37                | nW, All-in-One Trim-free Voltage/Current Reference without using Resistors and Amplifier | rs 14       |

| U  | 3.1                 |                                                                                          | 14          |

|    | 3.2                 | Proposed Voltage/Current reference                                                       | 15          |

|    | 5.2                 | 3.2.1 Temperature compensation of voltage/current reference                              | 16          |

|    |                     | 3.2.2 Process variation of voltage/current reference                                     | 17          |

|    | 3.3                 | Results and Discussion                                                                   | 18          |

|    | 3.4                 | Conclusion                                                                               | 22          |

| 4  |                     | 3-V, 593-pA Trim-free Duty-cycled All CMOS Current Reference for Ultra-Low Power Io7     | r.          |

| 4  |                     | ications                                                                                 | 23          |

|    | 4.1                 | Introduction                                                                             | 23<br>23    |

|    | 4.2                 | Design and analysis of the proposed Current reference                                    | 23<br>25    |

|    | 4.2                 | 4.2.1 Temperature Compensation of Proposed Current Reference                             | 25<br>25    |

|    |                     | 4.2.1 Process variation of the proposed current reference                                | 23<br>27    |

|    |                     |                                                                                          | 27          |

|    |                     |                                                                                          | 27<br>29    |

|    | 4.2                 |                                                                                          |             |

|    | 4.3                 | Result and discussion                                                                    | 31          |

|    | 4.4                 | Conclusion                                                                               | 34          |

### CONTENTS

| 5 | A 0. | 6V, 13n   | W, 0.0012%/V Line Sensitivity PVT - Invariant Voltage Reference without using |    |

|---|------|-----------|-------------------------------------------------------------------------------|----|

|   | Resi | stors and | d Amplifiers                                                                  | 35 |

|   | 5.1  | Introdu   | uction                                                                        | 35 |

|   | 5.2  | Design    | and Analysis of proposed voltage reference                                    | 37 |

|   |      | 5.2.1     | Current generator with improved line-sensitivity                              | 37 |

|   |      | 5.2.2     | Temperature Compensation of proposed Voltage reference                        | 39 |

|   |      | 5.2.3     | Line sensitivity of voltage reference                                         | 39 |

|   | 5.3  | Result    | s and Discussion                                                              | 40 |

|   | 5.4  | Conclu    | usion                                                                         | 43 |

| 6 | Cond | lusions   | and Future Work                                                               | 44 |

| 0 |      |           | Works                                                                         |    |

|   | 0.1  | 1 uture   | WOIRD                                                                         | 45 |

viii

## List of Figures

| Figure | I                                                                                              | Page |

|--------|------------------------------------------------------------------------------------------------|------|

| 1.1    | Market size revenue (in billion dollar) forecast worldwide from 2011 to 2027 [1]               | 2    |

| 2.1    | MOSFET operates in subthreshold region                                                         | 6    |

| 2.2    | Variations of voltage/current across temperatures                                              | 7    |

| 2.3    | Variation of Voltage/Current w.r.t supply voltage                                              | 8    |

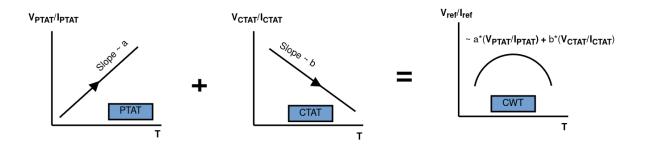

| 2.4    | Combination of PTAT and CTAT                                                                   | 10   |

| 2.5    | Combination of two PTAT sources with different slope                                           | 10   |

| 2.6    | Combination of two CTAT sources with different slope                                           | 11   |

| 2.7    | CTAT generator using diode connected MOSFET                                                    | 12   |

| 2.8    | (a) CTAT voltage generator using differential pair mosfet (b) PTAT current generator           |      |

|        | using Beta-multiplier                                                                          | 12   |

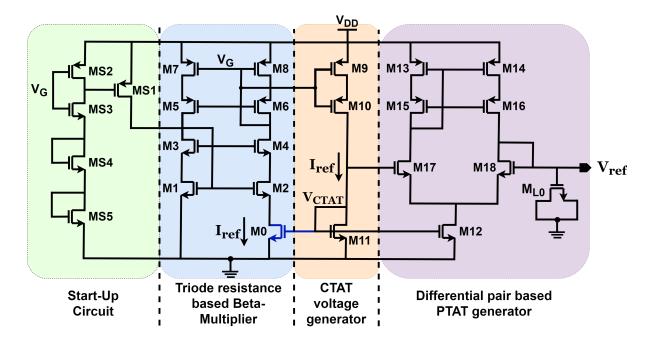

| 3.1    | Proposed voltage/current reference                                                             | 16   |

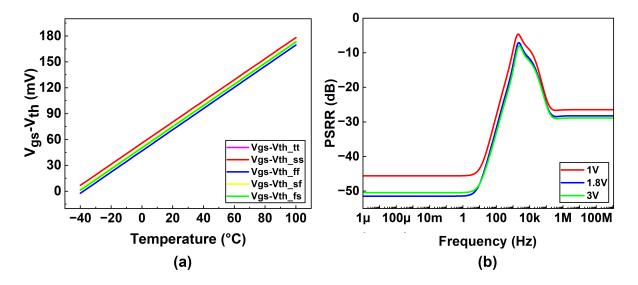

| 3.2    | (a) $V_{qs}$ - $V_{th}$ vs temperature across corners (b) PSRR of $V_{ref}$ w.r.t supply       | 18   |

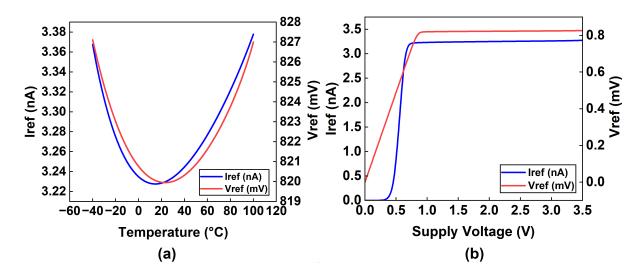

| 3.3    | (a) $V_{ref} \& I_{ref}$ vs Temperature (b) Supply sensitivity of $V_{ref} \& I_{ref}$         | 19   |

| 3.4    | Start-up time of (a) $V_{ref}$ and (b) $I_{ref}$                                               | 19   |

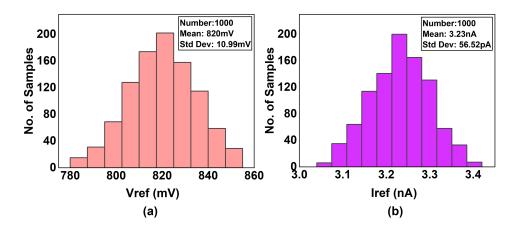

| 3.5    | Monte Carlo results for (a) $V_{ref}$ (b) $I_{ref}$ value at 27°C                              | 20   |

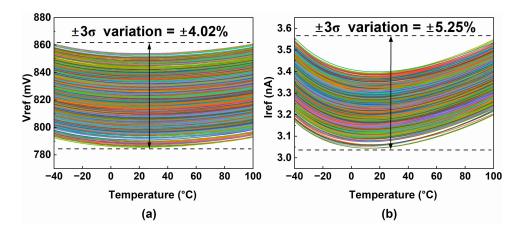

| 3.6    | $\pm 3\sigma$ variation of (a) $V_{ref}$ (b) $I_{ref}$                                         | 20   |

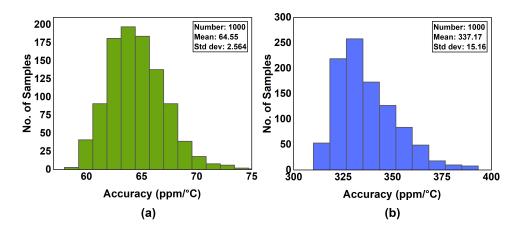

| 3.7    | Monte Carlo results for TC of (a) $V_{ref}$ (b) $I_{ref}$                                      | 20   |

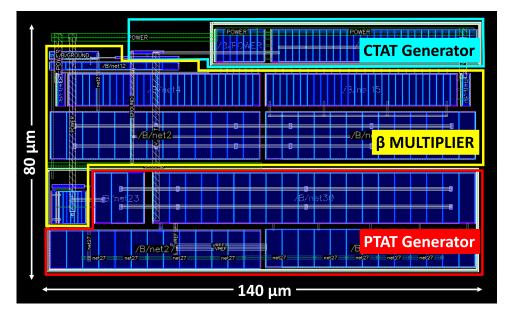

| 3.8    | Layout of proposed voltage/current reference                                                   | 22   |

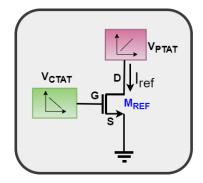

| 4.1    | Concept of Proposed Current reference                                                          | 23   |

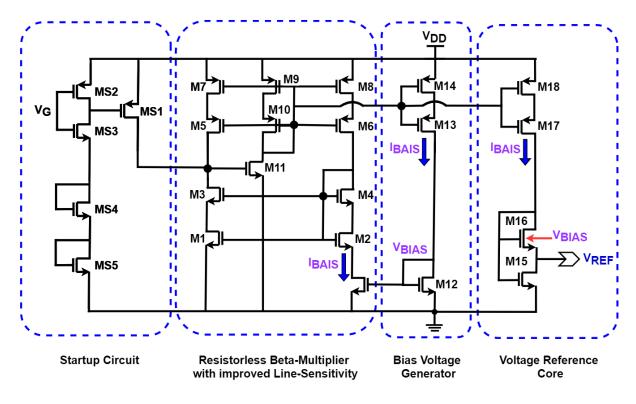

| 4.2    | Complete schematic of proposed current reference                                               | 24   |

| 4.3    | (a) Concept of subtracting two current references (b) Simulation of Subtracted current         |      |

|        | references                                                                                     | 27   |

| 4.4    | Duty-cycling schematic                                                                         | 30   |

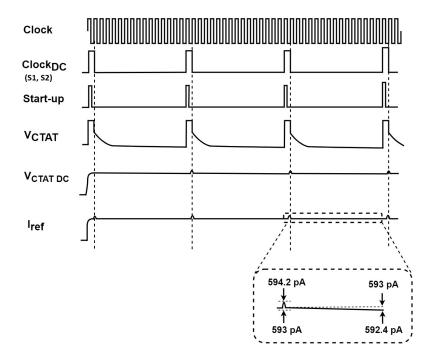

| 4.5    | The timing waveform of the current reference                                                   | 30   |

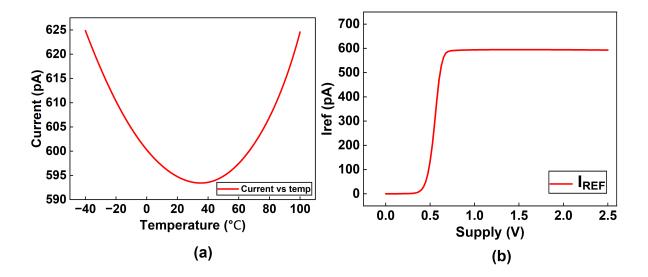

| 4.6    | (a) $I_{ref}$ vs Temperature (b) Supply sensitivity of $I_{ref}$                               | 32   |

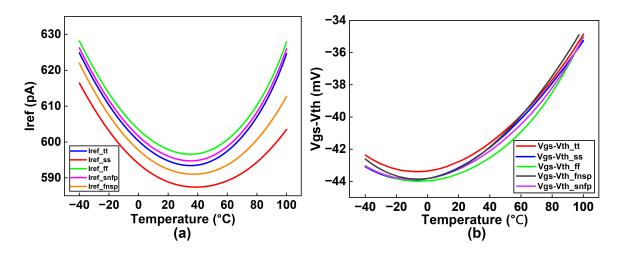

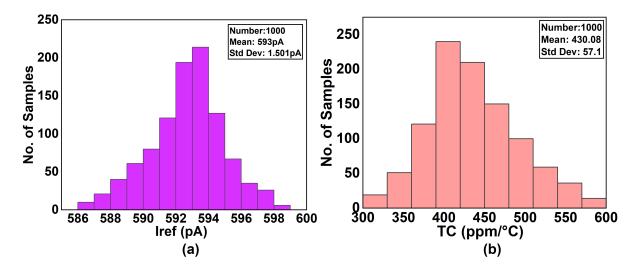

| 4.7    | Process corner plots for (a) $I_{ref}$ vs Temperature (b) $V_{GS}$ - $V_{TH}$ vs temperature   | 32   |

| 4.8    | (a) Monte Carlo results for (a) $I_{ref}$ @27°C (b) Temperature Coefficient of $I_{ref}$       | 33   |

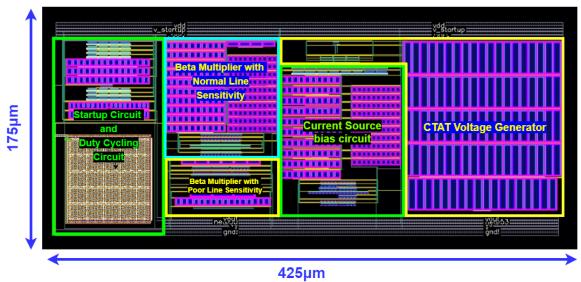

| 4.9    | Layout of the proposed current reference                                                       | 33   |

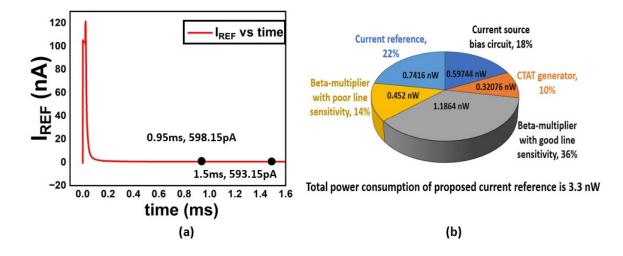

| 4.10   | (a) Startup time of $I_{ref}$ (b) The average power distribution of proposed current reference | 34   |

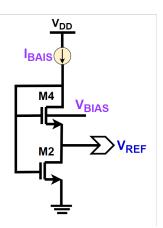

| 5.1    | Basic Concept of Proposed voltage reference                                                    | 35   |

| 5.2    | Proposed Voltage Reference                                                                     | 37   |

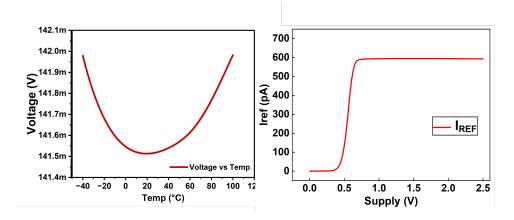

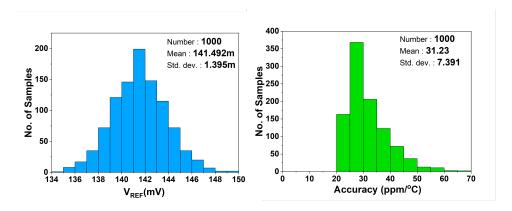

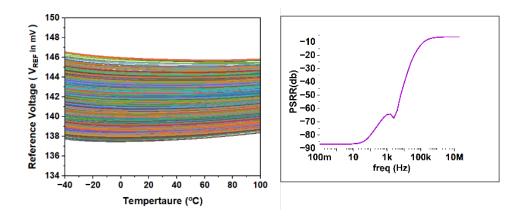

| 5.3 | (a) $V_{ref}$ & $I_{ref}$ vs Temperature (b) Supply sensitivity of $V_{ref}$ & $I_{ref}$ | 41 |

|-----|------------------------------------------------------------------------------------------|----|

| 5.4 | Monte Carlo results for (a) $V_{ref}$ (b) $I_{ref}$ value at 27°C                        | 41 |

| 5.5 | $\pm 3\sigma$ variation of (a) V <sub>ref</sub> (b) I <sub>ref</sub>                     | 41 |

## List of Tables

| Table |                                                           | Page |

|-------|-----------------------------------------------------------|------|

| 3.1   | Performance summary and comparison with the state-of-arts | 21   |

| 4.1   | Performance summary and comparison with the state of arts | 29   |

| 5.1   | Performance summary and comparison with other works       | 42   |

## Chapter 1

## Introduction

In the past seventy years, computing systems have undergone a remarkable transformation, transitioning from isolated interactions with computers to their ubiquitous integration into our daily lives. Initially, the collection of data on the internet relied heavily on human input and intervention. However, as the volume of data grew exponentially, there arose a need for a new paradigm where systems could autonomously interact with their environment. This marked the advent of the Internet of Things (IoT), a technological era characterized by the interconnection of everyday objects to networks. This connectivity revolutionizes how we interact with the world around us, creating new possibilities for innovative services and opportunities.

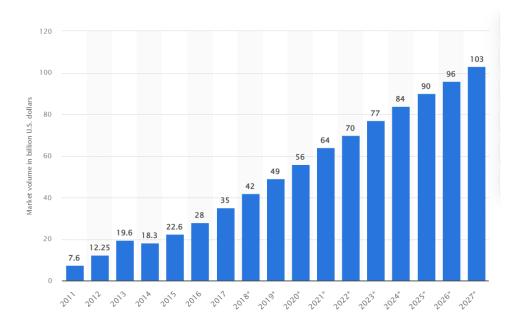

As the Internet of Things (IoT) grows, there is a greater need for devices that can operate efficiently. This demand for energy-efficient devices is driving the expansion of the IoT market, which has the potential to become the largest electronics market globally. With almost everything now connectable to the internet, the IoT market continues to expand rapidly. The graph below shows a steady increase in global active IoT connections, indicating a growing market size in billions of dollars over the years.

IoT applications rely heavily on analog circuit design to interface with the physical world. Analog circuits are crucial for tasks such as sensor signal conditioning, analog-to-digital conversion, power management, and wireless communication. These circuits play a vital role in ensuring that IoT devices can accurately sense, process, and communicate data in real-world environments. In general, these applications typically exhibit low-speed operation, low accuracy requirements, and low activity rates. However, they can greatly benefit from enhanced energy efficiency, which enables increased portability, reduced complexity, and cost savings. Researchers around the globe are confronted with the complex task of modifying different Internet of Things (IoT) subsystems, such as sensing networks, biasing networks, and radio frequency transmission circuitry, to accommodate the evolving requirements of IoT devices. To tackle these challenges, this thesis presents a comprehensive set of circuit-level techniques and system-level optimizations tailored to meet the diverse demands of emerging IoT applications.

Figure 1.1: Market size revenue (in billion dollar) forecast worldwide from 2011 to 2027 [1]

### **1.1** Motivation behind low-power Analog circuits for IoT applications

The motivation behind low-power analog circuits for IoT applications stems from the unique requirements of IoT devices. IoT devices are often deployed in remote or hard-to-reach locations and are powered by batteries or energy harvesters. As such, they must operate efficiently to prolong battery life or operate in energy-constrained environments. Low-power analog circuits are essential in IoT devices for several reasons:

- Energy Efficiency: Low-power analog circuits help minimize energy consumption, extending the operational life of battery-powered IoT devices and reducing the need for frequent battery replacements. Energy-efficient circuits are often more reliable than their high-power counterparts. They generate less heat, which can reduce the risk of component failure and ensure consistent performance over time.

- **Cost-Effectiveness**: By reducing power consumption, low-power analog circuits can lead to cost savings, as smaller batteries or energy harvesters can be used.

- Scalability: Low power Analog circuits are crucial for the scalability of IoT deployments. As the number of connected devices grows, the demand for energy-efficient solutions becomes increasingly important to manage power consumption effectively.

This thesis aims to delve into the intricate design considerations, innovative methodologies, and comprehensive system-level optimizations essential for Low Power Analog Circuit Design in IoT and Biomedical Applications. It investigates the unique challenges posed by these fields, ranging from the imperative of extended battery life and effective energy harvesting in IoT devices to the stringent power constraints and biocompatibility prerequisites in biomedical scenarios.

By thoroughly examining these design principles, the significance of this thesis emerges. It addresses the urgent needs of our progressively interconnected world and the constantly evolving realm of healthcare technology, where efficient, low-power analog circuits have the potential to not only augment device functionality but also enhance the quality of life for individuals. This endeavor aims to unlock the full potential of IoT and Biomedical Applications, offering solutions that are not only technologically advanced but also environmentally sustainable and centered on human well-being.

## **1.2 Thesis Organisation**

In this thesis, we introduced ultra-low power analog circuits designed for IoT and biomedical applications, focusing on the importance of voltage and current references. These references are critical in IoT systems, requiring them to adjust their power consumption to meet new demands. In systems with analog-to-digital converters (ADCs), voltage and current references play a crucial role in calibrating the ADCs for accurate digitization of analog signals. They are also essential in circuits requiring temperature compensation, ensuring stable performance across varying temperatures. Additionally, voltage and current references are used in biasing networks to set component operating points, ensuring proper circuit functionality. It is essential for these references to operate accurately over a wide temperature range without the need for external trimming circuits.

Chapter 2 of this thesis presents the foundational knowledge required for designing voltage and current references tailored for ultra-low-power IoT and biomedical applications. The chapter explores diverse techniques for temperature compensation, improving supply sensitivity, and ensuring process invariance for these references. Furthermore, it examines the essential parameters and specifications relevant to analog circuits, such as voltage and current references, highlighting their significance in circuit design.

Chapter 3 introduces a novel All-in-One low-power, Trim-free Voltage/Current Reference without using Resistors and Amplifiers designed specifically for IoT and biomedical applications. The voltage reference is created through the combination of Complementary to Absolute Temperature (CTAT) and Proportional to Absolute Temperature (PTAT) voltages, while the current reference utilizes a MOSFET in its linear region to function as a resistor, minimizing power consumption without increasing the device's form factor. Implemented in a 90nm CMOS process, the proposed voltage/current reference achieves an output voltage and current of 820mV and 3.23nA, respectively. Notably, the reference design does not require trimming, exhibiting a process variation of 1.34% ( $\sigma/\mu$ ) / 1.75% ( $\sigma/\mu$ ) and a temperature coefficient of 62ppm/°C / 332ppm/°C over a wide temperature range from -40oC to 100oC. The line sensitivity of the voltage/current reference stands at 0.296%/V / 0.414%/V across a broad

supply range of 1V to 3.5V. Occupying a minimal area of 0.0112mm<sup>2</sup>, the total power consumption of the circuit design is measured at 37nW under typical conditions of 27°C and 1V supply.

Chapter 4 introduces a sub-1V, sub-nA current reference with the absence of large resistors, hence occupying a small area. A 593pA temperature-independent current reference is generated by incorporating a CTAT gate to source voltage and a PTAT drain to source voltage in an NMOS-based subthreshold-biased circuit. Without trimming, the proposed reference current has  $\pm 0.75\%$  variation across the process corners. The proposed circuit is implemented in a 90nm CMOS process having a temperature coefficient of 378ppm/oC over a temperature range of -40°C to 100°C and a line sensitivity of 0.198%/V in a range of supply voltage from 0.8V to 2.8V. A duty-cycle technique is applied to enable 1% duty-cycling of the CTAT generator, resulting in a reduction in power consumption of the overall circuit. The area occupied by the resistor-less circuit is 0.0286mm<sup>2</sup>, while the total power consumption of the design with duty-cycling technique is 4nW at the typical corner of 27°C and 0.8V supply.

Chapter 5 presents a low-voltage, low-power PVT-invariant voltage reference with excellent line sensitivity for IoT and biomedical applications. By applying a bias current( $I_{bias}$ ) in NMOS-based composite pair and bias voltage( $V_{bias}$ ) at the body of NMOS to get the temperature-compensated voltage reference over a wide temperature range. The proposed design implemented in 180nm CMOS process gives an outputs of 141mW which is independent of process, voltage and temperature. Without trimming, the process variation of proposed design is  $1.51\%(\sigma/\mu)$  and the temperature coefficient of proposed voltage reference is  $23ppm/^{\circ}C$  over a wide temperature range of  $-40^{\circ}C$  to  $100^{\circ}C$ . For a supply voltage ranging from 0.6V - 2.1V the line sensitivity of the reference is 0.0012%/V. The simulated results shows that the proposed voltage reference could operate on a minimum supply of 0.6V and the power supply rejection ratio at 1-Hz is ... .The area occupied by the total circuit is  $0.0085mm^2$ , while the total power consumption of the design is 14.2nW at the typical corner of  $27^{\circ}C$  and 0.6V supply.

Finally in Chapter 6, the conclusions drawn from the research done so far are presented. Additionally, potential areas for further improvement and future research directions are discussed.

Chapter 2

## **Literature Review**

## 2.1 Introduction

The field of microelectronics is witnessing exciting developments in ultra-low power LSIs, offering significant promise for various applications demanding power efficiency. These LSIs hold particular relevance for portable mobile devices, implantable medical devices, and smart sensor networks [2]. Given the anticipated deployment in environments with limited energy sources, such as microbatteries or energy scavenging devices, these devices must operate on ultra-low power levels, typically in the range of a few microwatts or less [3].

A critical milestone in advancing these LSIs is the development of voltage and current reference circuits capable of ultra-low current operation, often in the realm of several tens of nanoamperes or less, corresponding to sub-microwatt operation. To achieve such remarkable power efficiency, these circuits must operate in the subthreshold region, where the gate-source voltage of MOSFETs falls below the threshold voltage [4, 5].

## 2.2 Subthreshold region(Weak inversion region) of MOSFETs

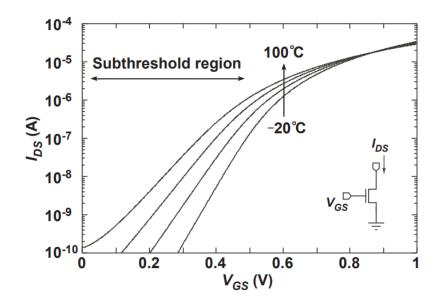

The subthreshold region in MOSFET operation is a crucial domain for achieving ultra-low power consumption in integrated circuits. In this region, the gate-source voltage of the MOSFET is lower than the threshold voltage, resulting in a low drain-source current. This region is particularly important for applications where minimizing power consumption is paramount, such as in IoT devices, biomedical implants, and energy harvesting systems. By operating in the subthreshold region, MOSFETs can achieve high energy efficiency, making them ideal for applications requiring long battery life or operation on limited power sources. However, designing circuits to operate in the subthreshold region poses challenges, including increased sensitivity to process variations and temperature effects, requiring careful optimization and design techniques.

The subthreshold region of a MOSFET occurs when the gate-source voltage falls below the threshold voltage. In this regime, a small leakage current, known as subthreshold current, flows through the

MOSFET. This current exhibits an increasing exponential relationship with the gate-source voltage and typically operates at the nanoampere level. The subthreshold drain current  $(I_{DS})$  in a MOSFET follows an exponential relationship with both the gate-source voltage  $(V_{GS})$  and the drain-source voltage  $(V_{DS})$  [6]. Specifically, it is given by:

$$I_{DS} = K_n \frac{W}{L} \left(\eta - 1\right) V_T^2 \exp\left(\frac{V_{GS} - V_{TH}}{\eta V_T}\right) \left(1 - \exp\frac{-V_{DS}}{V_T}\right)$$

(2.1)

where  $K_n = \mu_n C_{ox}$ ,  $V_{TH}$  represents the threshold voltage of the transistor,  $V_T$  is the thermal voltage and  $\eta$  is the sub-threshold slope constant. Fig. 2.1 shows the Ids vs vgs characteristics of a NMOS operating in subthreshold region at different temperature range.

Figure 2.1: MOSFET operates in subthreshold region

When the vds of mosfet operates in subthreshold region is greater than 4 times of thermal voltage i.e the current obtained through the mosfet is independent of Vds and is given by :

$$I_{ref} = K_n \frac{W}{L} \left(\eta - 1\right) V_T \exp\left(\frac{V_{GS} - V_{TH}}{\eta V_T}\right)$$

(2.2)

## 2.3 Process, voltage and temperature independent Analog circuits

Process, voltage, and temperature (PVT) independent analog circuits are essential components in modern integrated circuit design, particularly for applications requiring high reliability and performance across varying operating conditions. These circuits are designed to maintain consistent functionality and performance regardless of manufacturing process variations, supply voltage fluctuations, or temperature changes. Achieving PVT independence often involves sophisticated design techniques, such as using compensation circuits to counteract process variations, designing circuits with wide supply voltage

ranges, and employing temperature compensation methods. PVT independent analog circuits are particularly valuable in applications where precise and stable analog signal processing is critical, such as in sensor interfaces, data converters, and communication systems.

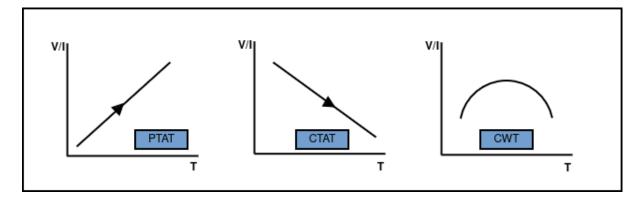

#### 2.3.1 Temperature variation

Temperature-invariant analog circuits are crucial components in electronic systems, ensuring stable performance across a wide range of operating temperatures. These circuits are designed to maintain consistent functionality and performance regardless of temperature fluctuations. The parameter used for temperature variation is the temperture coefficient. In analog circuits, the temperature coefficient (TC) refers to the rate of change of a circuit parameter (such as voltage, current, or resistance) with respect to temperature. It is expressed in units of the parameter per degree Celsius (e.g., ppm/°C for voltage or current). In the realm of analog circuits, the behavior of certain parameters such as voltage or current with respect to temperature is of particular interest. When the parameter increases proportionally with an increase in temperature, it is referred to as Proportional to Absolute Temperature (PTAT). Conversely, if the parameter decreases as temperature rises, it is termed Complementary to Absolute Temperature (CTAT). Finally, when the parameter remains constant regardless of temperature variations, it is known as Constant with respect to Temperature (CWT). Understanding these temperature-dependent behaviors is crucial in designing circuits. Fig. 2.2 shows the parameter nature with predictable and stable performance across varying thermal conditions.

Figure 2.2: Variations of voltage/current across temperatures

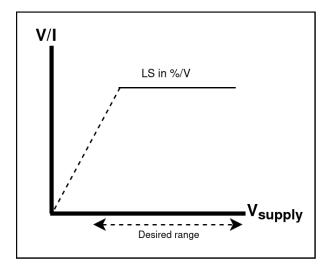

#### 2.3.2 Voltage variation

Voltage-invariant analog circuits are fundamental components in electronic systems, designed to maintain consistent functionality despite fluctuations in the supply voltage. These circuits are crucial for ensuring stable performance across a wide range of operating conditions, as variations in the supply voltage can significantly impact the behavior of analog circuits. we expressed the voltage variation in terms of line sensitivity. Line sensitivity, refers to the change in output voltage of a circuit in response

to variations in the supply voltage. It is a critical parameter in analog circuits, especially in applications where the stability of the output voltage is crucial. Line sensitivity is typically expressed in percentage change in output voltage per volt change in supply voltage (%/V). A lower line sensitivity indicates that the circuit's output voltage is less affected by changes in the supply voltage, which is desirable for maintaining stable circuit operation. In this thesis we applied line sensitivity improving techniques to improve the variation of output quantities i.e voltgae or current with respect to supply voltage.

Figure 2.3: Variation of Voltage/Current w.r.t supply voltage

#### 2.3.3 Process Variation

Process variation is a significant challenge in analog circuit design, stemming from manufacturing inconsistencies that lead to differences in the electrical characteristics of individual components. These variations can result in deviations from the intended circuit behavior, affecting performance metrics such as gain, bandwidth, and power consumption. To mitigate the impact of process variation, designers employ various techniques, including layout strategies, statistical design methodologies, and calibration circuits. Additionally, advances in semiconductor manufacturing processes, such as improved process control and modeling, have helped reduce process variation. Despite these efforts, managing process variation remains a critical consideration in analog circuit design, particularly in applications requiring high precision and reliability.

Process variations can be classified into two categories: i.e., within-die (WID) (intra-die) variation and die-to-die (D2D) (inter-die) variation .The WID variation is caused by mismatches between transistor parameters within a chip and affects the relative accuracy of the parameters. In contrast, the D2D variation affects the absolute accuracy of transistor parameters between chips [7, 8, 9, 10]. Process variations can also affect the threshold voltage of a MOSFET. Variations in doping concentrations, oxide thickness, and other fabrication parameters can lead to variations in the threshold voltage across

different transistors on the same chip. These variations can impact circuit performance and may require additional design considerations to ensure reliable operation.

#### 2.3.4 Fundamental Analog blocks : Voltage and current reference

Voltage and current reference circuits serve as foundational elements in microelectronics, playing a crucial role in ensuring the reliable performance of analog, digital, and mixed-signal circuit systems. These circuits are primarily characterized by their ability to maintain stable bias voltages and currents, which are essential for the proper functioning of various components like operational amplifiers, comparators, AD/DA converters, oscillators, and PLLs. To achieve this stability, bandgap reference circuits utilizing CMOS-based vertical bipolar transistors have traditionally been the go-to choice in CMOS LSIs, providing a constant and precise reference voltage and current.

#### 2.3.4.1 Generation of Voltage and current reference

Generating a voltage/current reference typically entails either combining two quantities with opposite temperature dependencies or subtracting two quantities with similar temperature dependencies resulting into a voltage and current reference with no variation of current and voltage with temperature.

#### Case 1: Combination of Voltage/Current with opposite temperature dependencies

This method approach is to combine two quantities that have opposite temperature dependencies. This means that as one quantity increases with temperature, the other decreases, and vice versa. By combining these two quantities, the overall effect cancels out the temperature variations, resulting in a stable output. For example, in a voltage reference circuit, one can combine a voltage source that increases with temperature (PTAT) with a voltage source that decreases with temperature (CTAT). By appropriately choosing and combining these sources, the temperature-dependent variations can cancel each other out, resulting in a stable output voltage over a wide temperature range. In a current reference circuit, a similar principle applies. By combining two current sources with opposite temperature coefficients, the variations in one source can offset the variations in the other, leading to a stable output current despite changes in temperature. Figure explain the generation of voltage/current reference by combining two opposite temperature dependecies i.e PTAT and CTAT with a slope of a and b respectivily to get  $V_{ref}$

Figure 2.4: Combination of PTAT and CTAT

#### Case 2: Combination of Voltage/Current with same temperature dependencies

The second approach to generating a voltage or current reference involves subtracting two quantities with similar temperature dependencies. This method relies on the fact that some components or materials exhibit temperature-dependent characteristics that change in a predictable manner with temperature. For example, in a voltage reference circuit, one can use two voltage sources with similar positive temperature coefficients (PTAT) with different slope or with similar negative temperature coefficient (CTAT) with different slope or woltage source from the other, the temperature-dependent variations can be made to cancel out, resulting in a stable output voltage over a wide temperature range. Similarly, in a current reference circuit, two current sources with similar temperature coefficients can be subtracted from each other to achieve a stable output current despite changes in temperature. The Figure 2.5 and 2.6 shows the explaination as discussed above i.e

$$V_{ref}/I_{ref} = \left\{ \begin{array}{l} a * V_{PTAT1} / I_{PTAT1} - b * V_{PTAT2} / I_{PTAT2} \\ a * V_{CTAT1} / I_{CTAT1} - b * V_{CTAT2} / I_{CTAT2} \end{array} \right\}$$

Figure 2.5: Combination of two PTAT sources with different slope

Figure 2.6: Combination of two CTAT sources with different slope

#### 2.3.5 Methods of generating PTAT and CTAT voltage/current

Generating Proportional to Absolute Temperature (PTAT) and Complementary to Absolute Temperature (CTAT) voltage and current references is crucial in analog circuit design, especially for applications sensitive to temperature variations. A commonly used method to generate a PTAT voltage involves utilizing the base-emitter voltage of a bipolar junction transistor (BJT), which exhibits a positive temperature coefficient. By biasing the BJT appropriately, its base-emitter voltage can serve as a PTAT voltage reference. Conversely, for CTAT voltage generation, components like diodes or resistors with negative temperature coefficients can be combined with PTAT sources. Similar principles apply to current reference generation, where the temperature-dependent voltage across a resistor or diode is leveraged to create a PTAT or CTAT current reference. These methods necessitate meticulous component selection and precise circuit design to achieve the desired temperature characteristics for voltage and current references. Here are the some PTAT and CTAT current/voltage circuits used in our thesis.

#### **Circuit 1: CTAT voltage using diode connected MOSFET**

CTAT (Complementary to Absolute Temperature) voltage generation using a diode-connected MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) is a technique commonly employed in analog circuit design [11]. In this method, the MOSFET is biased in the Subthreshold-saturation region, where the drain and gate are connected together, effectively forming a diode-like structure. The voltage across this diode-connected MOSFET exhibits a negative temperature coefficient, meaning that it decreases with increasing temperature.

The threshold voltage  $(V_{th})$  exhibits a complementary to absolute temperature (CTAT) behavior, expressed as  $V_{th0} - k_1 T$ , where  $V_{th0}$  is the nominal threshold voltage, and  $k_1$  represents the slope of the threshold voltage. The term  $\mu_n$  is directly proportional to  $T^{-3/2}$  [12, 13], causing the term  $\eta V_T \ln \left(\frac{I}{\mu_n C_{ox}(\eta-1)V_T^2}\right)$  to be proportional to  $\ln(T^{-1/2})$ , assuming I remains constant with temperature. Despite being a weak function of temperature, the predominant CTAT nature of  $V_{th}$  extends to  $V_{GS}$ .

$$V_{GS} = V_{th} + \eta V_T \ln\left(\frac{I}{\mu_n C_{ox}(\eta - 1)V_T^2}\right)$$

(2.3)

Figure 2.7: CTAT generator using diode connected MOSFET

#### Circuit 2: CTAT/PTAT voltage generation using single block

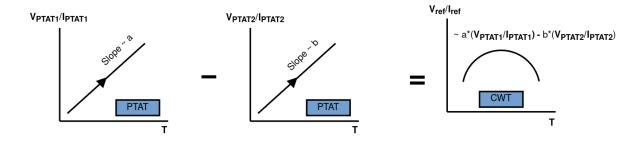

As shown in Fig. 2.8, the CTAT generator is applied as an input to the PTAT/CTAT generator and biased with the reference current ( $I_{ref}$ ). Since the MOSFET operates in the sub-threshold region,  $V_{GG}$  can be expressed as follows:

Figure 2.8: (a) CTAT voltage generator using differential pair mosfet (b) PTAT current generator using Beta-multiplier

$$V_{GG} = V_{ref} - V_{CTAT} = V_{GS,M18} - V_{GS,M17}$$

=  $V_{TH} + \eta V_T \ln \left(\frac{I_{M18}}{K_{M18}I_0}\right) - V_{TH} - \eta V_T \ln \left(\frac{I_{M17}}{K_{M17}I_0}\right)$  (2.4)

=  $\eta V_T \ln \left(\frac{K_{M14}K_{M17}}{K_{M13}K_{M18}}\right)$

Where,  $I_0 = \mu C_{OX}(\eta - 1)V_T^2$  is a process dependent parameter.  $K_{M17}$ ,  $K_{M18}$ ,  $K_{M13}$  and  $K_{M14}$  are the aspect ratios of the NMOS differential pair and the PMOS current mirrors respectively. If  $K_{M14}K_{M17} > K_{M13}K_{M14}$  the  $V_{GG}$  will PTAT in nature whereas,  $K_{M14}K_{M17} < K_{M13}K_{M14}$  the voltage  $V_{GG}$  is CTAT in nature.

#### Circuit 3: PTAT current generation using beta multiplier circuit

Proportional to Absolute Temperature (PTAT) current generation using a beta multiplier circuit with Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) is a technique commonly employed in analog circuit design for temperature-independent current generation. The circuit utilizes the temperature-dependent threshold voltage of MOSFETs to create a current that varies proportionally with absolute temperature[14]. The beta multiplier circuit with MOSFETs typically consists of two MOSFETs, one acting as a diode-connected device and the other as a current mirror. By appropriately biasing the MOSFETs and adjusting the resistor values, the circuit can produce a PTAT current that compensates for temperature variations, making it suitable for applications requiring stable and accurate current references over a wide temperature range. The figures shows the operation of PTAT current using beta multiplier.

## Chapter 3

## A 37nW, All-in-One Trim-free Voltage/Current Reference without using Resistors and Amplifiers

#### **3.1 Introduction**

In recent years, significant progress has been made in developing low-power designs that are essential for battery-powered devices like wearables and IoT devices, where power consumption is a critical factor. Voltage/current references being essential components of any IoT system should also scale their power to satisfy the new requirements. Moreover, it is highly desirable for these references to operate over a wide temperature range with good accuracy and line sensitivity, without incorporating external trimming circuits. Trim-free designs eliminate the need for external calibration, reduce manufacturing costs and improve the circuit's reliability. Also, it is beneficial to have both the reference circuitry (voltage and current) to be integrated into a single block.

The voltage reference is a crucial component in the construction of analog, digital, and mixed-signal circuit systems. For operational amplifiers, comparators, and AD/DA converters to work properly, a constant reference voltage is needed. Voltage references are conventionally realized using BJTs and are called bandgap references (BGR) [15, 16]. Although the generated voltage in BGRs is highly resilient to process, supply, and temperature (PVT) variations, they consume power in the  $\mu$ W range and require a high supply voltage. Recently, CMOS subthreshold voltage references have received much attention since they operate at low supply voltages and consume very low power [17, 18, 19, 20]. [17] proposes a sub- $\mu$ W voltage reference using MOSFETs and resistors. However, high resistance values used for lowering the power consumption have a direct tradeoff with the silicon area. [18] presents a resistor-less voltage reference with nW power consumption, but external trimming circuitry is required to correct the process variation of the design.

[19] proposes a CMOS-based voltage reference having power consumption in nW without using resistors and trimming circuits, but the process variation ( $\sigma/\mu$ ) of the design is 7%. To get further power reduction [20] proposes a pW voltage reference. However, it reports no functionality at negative temperatures. This constraint is mainly due to the exponential dependency of subthreshold leakage

on temperature. Also, they use native oxide devices (NVT MOSFETs), which are not provided by many foundries [21]. The conventional approach for generating current references involves variants of the beta multiplier, utilizing the V/R principle with opamps to effectively compensate the temperature coefficients of both resistance and voltage [22, 23].

However, resistance-based designs require an inconsiderably higher area to scale the power consumption of the pW and nW regime. To mitigate this issue, [24] replaces the resistor in the betamultiplier with a MOSFET in deep triode to achieve power consumption in nW but at the cost of high process variation and large voltage supply (Min. supply = 1.3V). [25] proposes a current reference with a lower supply and nW power consumption. However, the process variation ( $\sigma/\mu$ ) of the design is >10%. [26] improves the process variation of the current reference with a process tracking circuit but the power consumption, line sensitivity and temperature range make it unsuitable for low-power IoT applications. Design [27] proposes a trim-free nW current reference with a low process variation of 8.8% (6 $\sigma$ ). However, the architecture works from a minimum supply of 1.5V. [28, 29] proposes pico-watt current references using tunneling currents, although these references require lower area, the susceptibility of tunneling currents to tox variations [30] (>600% across process corners) necessitates extensive trimming and increases the cost. References [31, 32, 33] explain voltage and current reference in a single block. [31] proposes nW voltage/current reference using resistors and amplifiers whereas, using amplifiers incurs additional design complexity like offset, power consumption, etc. [32] does not use an amplifier but requires a trimming circuit to improve process variation. [33] consumes power in pW but uses native oxide devices and trimming circuits.

This thesis presents a 37nW, trim-free voltage/current reference with a wide temperature range of -40°C to 100°C without using resistors, amplifiers and native oxide devices. The rest of the thesis is structured as follows: Section 3.2 describes the proposed voltage/current reference. Section 3.3 presents the simulated results and conclusions are drawn in Section 3.4.

## 3.2 Proposed Voltage/Current reference

The architecture of the proposed circuit is shown in Fig. 3.1. All the MOSFETs except M0 are in the subthreshold saturation region. The MOS resistor M0 is operated in a strong inversion, deep-triode region. The design consists of a triode resistance-based Beta-multiplier, a CTAT generator and a PTAT generator. A combination of triode resistance-based Beta-multiplier and CTAT generator results in a current reference [27] whereas, the PTAT and CTAT generator compensates for any variation of the generated voltage reference. Moreover, the generated reference current ( $I_{ref}$ ) is used to bias the PTAT generator.

A capacitor ( $C_{eq}=2.17\text{pF}$ ) implemented using a thick oxide device ( $M_{L0}$ ) is connected at the output terminal to have a better power supply rejection ratio (PSRR) at higher frequencies. A start-up circuit [34] is added to avoid any degenerative conditions.

Figure 3.1: Proposed voltage/current reference

#### **3.2.1** Temperature compensation of voltage/current reference

In the circuit, the current  $I_{ref}$  is generated by MOS resistor M0 with gate-source voltage  $V_{GS,M0}$  and drain-source voltage  $V_{DS,M0}$ . When MOSFET M0 operates in strong inversion and deep triode region ( $V_{GS} - V_{TH} > V_{DS}$ ), the current through M0 is given by

$$I_{ref} = K_n \left(\frac{W}{L}\right) \left(V_{GS,M0} - V_{TH}\right) V_{DS,M0}$$

(3.1)

Where,  $K_n = \mu_n C_{ox}$ ,  $\frac{W}{L}$  is the aspect ratio of the MOSFET M0 and  $V_{DS,M0} = V_{GS,M1} - V_{GS,M2}$ . To analyze the temperature behavior of reference current  $(I_{ref})$ , differentiating (3.1) with respect to temperature (T) we get

$$\frac{\partial I_{ref}}{\partial T} = K_n \left(\frac{W}{L}\right) V_{DS} \left(\frac{\partial V_{GS}}{\partial T} - \frac{\partial V_{TH}}{\partial T}\right) + K_n \left(\frac{W}{L}\right)$$

$$\left(V_{GS} - V_{TH}\right) \left(\frac{\partial V_{DS}}{\partial T}\right) + \frac{\partial K_n}{\partial T} (V_{GS} - V_{TH}) V_{DS} \quad (3.2)$$

Therefore, the circuit is designed in such a way that the CTAT term  $K_n$  gets compensated by the PTAT terms  $V_{DS,M0}(=\eta V_T \ln n)$  and ( $V_{GS} - V_{TH}$ ) as shown in Fig. 3.2(a) to obtain the temperature-compensated reference current ( $I_{ref}$ ).

The PTAT generator along with a CTAT generator and a current reference is required to obtain a temperature-compensated voltage reference  $(V_{ref})$ .

The CTAT generator is applied as an input to the PTAT generator and biased with the reference current  $(I_{ref})$ . Since the MOSFET operates in the subthreshold region,  $V_{GG}$  can be expressed as follows:

$$V_{GG} = V_{ref} - V_{CTAT} = V_{GS,M18} - V_{GS,M17}$$

=  $V_{TH} + \eta V_T \ln\left(\frac{I_{M18}}{K_{M18}I_0}\right) - V_{TH} - \eta V_T \ln\left(\frac{I_{M17}}{K_{M17}I_0}\right)$  (3.3)

=  $\eta V_T \ln\left(\frac{K_{M14}K_{M17}}{K_{M13}K_{M18}}\right)$

Where,  $I_0 = \mu C_{OX}(\eta - 1)V_T^2$  is a process dependent parameter.  $K_{M17}$ ,  $K_{M18}$ ,  $K_{M13}$  and  $K_{M14}$  are the aspect ratios of the NMOS differential pair and the PMOS current mirrors respectively.

$$V_{ref} = V_{GG} + V_{CTAT} = \eta V_T \ln \left( \frac{K_{M14} K_{M17}}{K_{M13} K_{M18}} \right) + V_{th} + \eta V_T \ln \left( \frac{I_{ref}}{I_0} \right) = V_{th} + \eta V_T \ln \left( \frac{K_{M14} K_{M17} I_{ref}}{K_{M13} K_{M18} I_0} \right)$$

(3.4)

Considering the temperature coefficient,  $V_{ref}$  can be given as:

$$\frac{\partial V_{ref}}{\partial T} = \frac{\partial V_{th}}{\partial T} + \eta \frac{k}{q} \ln \left( \frac{K_{M14} K_{M17} I_{ref}}{K_{M13} K_{M18} I_0} \right)$$

(3.5)

A temperature-compensated voltage can be obtained by appropriately sizing the transistors M13, M14, M17 & M18.

#### 3.2.2 Process variation of voltage/current reference

To study the effect of process variation on the voltage/current reference, one needs to check the process variant terms present in the equations of  $V_{ref}$  and  $I_{ref}$ . Eq.1 shows that threshold voltage is mainly responsible for process variation, where  $V_{GS,M0} = V_{TH} + \eta V_T \ln(I_{ref}/I_0)$ . After substituting the value of  $V_{GS,M0}$  in (3.1):

$$I_{ref} = \mu_n C_{ox} \left(\frac{W}{L}\right) (V_{TH} + \eta V_T \ln\left(\frac{I_{ref}}{I_0}\right) - V_{TH}) V_{DS,M0}$$

$$= \mu_n C_{ox} \left(\frac{W}{L}\right) \eta V_T \ln\left(\frac{I_{ref}}{I_0}\right) V_{DS,M0}$$

(3.6)

Here,  $V_{TH}$  cancellation takes place, which ultimately improves the process variation of the reference current. The value of  $V_{GS}$  -  $V_{TH}$  as shown in Fig. 3.2(a) at different process corners has minimal variation, demonstrating the reference current is less susceptible to process.

From 3.4, it can be observed that the expression of  $V_{ref}$  has three process variant terms  $V_{TH}$ ,  $\eta$ , and  $I_{ref}$ .  $V_{TH}$  contributes the most and  $I_{ref}$  contributes the least amongst these. The input to the PTAT generator i.e.  $V_{CTAT}$  voltage is generated by passing  $I_{ref}$  into a diode-connected MOSFET. In any

process corner, if the  $V_{TH}$  increases, the corresponding current decreases, and as  $I_{ref}$  decreases the drain to source voltage  $V_{DS}$  (= $\eta V_T \ln(n)$ ) across the triode MOSFET M0 also decreases meaning that,  $\eta$  decreases for both PTAT terms.  $\eta$  is the subthreshold slope factor which depends on the gate oxide and depletion layer capacitances [35]. So, the process variation of  $V_{TH}$  is inversely related to the process variation of  $\eta$  and  $I_{ref}$ . The small process variation of  $I_{ref}$  along with the multiplication constant  $(K_{M14}K_{M17}/K_{M13}K_{M18})$  that amplifies the process variation of  $\eta$ , mitigates the  $V_{TH}$  variation to a great extent, resulting in smaller process variation of the reference voltage  $(V_{ref})$ .

Figure 3.2: (a)  $V_{gs}$  -  $V_{th}$  vs temperature across corners (b) PSRR of  $V_{ref}$  w.r.t supply

## 3.3 Results and Discussion

The proposed voltage/current reference is designed and implemented in a 90nm CMOS process. Fig. 3.2(b) shows the PSRR at DC for the voltage reference at 1V, 1.8V, and 3V are -48dB, -52dB, and -51dB respectively. Fig. 3.3(a) shows temperature-compensated voltage and current reference plots; it depicts temperature coefficients (TC) of 62ppm/°C and 332pm/°C respectively for the temperature range of -40 to 100°C. The nominal value of the current and voltage reference is 3.23nA and 0.820V respectively. Fig. 3(b) shows the supply sensitivities of voltage and current references as 0.296%/V and 0.414%/V respectively for the supply range of 1 to 3.5V. As this architecture contains a self-biased loop, to avoid any degenerative conditions, a start-up circuit is added. Fig. 3.4 shows the 99% settling times for the voltage and current reference to be 11.73ms and 11.84ms, respectively. The statistical results for voltage and current reference are presented in Fig. 3.5 Using Monte Carlo simulation with 1000 samples the observed mean and standard deviation from Fig. 3.5(a) for the voltage reference are 820mV and 10.99mV respectively, which results in process variation ( $\sigma/\mu$ ) of 1.34%. Fig. 3.5(b) illustrates the Monte Carlo results for the current reference. The mean and standard deviation are 3.23nA and 56.52pA respectively, resulting in process variation ( $\sigma/\mu$ ) of 1.75%. Fig. 3.6(a) shows the Monte Carlo results for V<sub>ref</sub> over the temperature range of -40 to 100°C, from which  $3\sigma$  variation of ±4.02% can be observed. Similarly, from Fig. 3.6(b) ± $3\sigma$  variation of ±5.25% can be observed for the  $I_{ref}$ w.r.t temperature. Fig. 3.7(a) shows the Monte Carlo results (1000 points) for the TC of V<sub>ref</sub>. The observed mean and the standard deviation are 64.55ppm/°C and 2.564ppm/°C, respectively. Similarly, Fig. 3.7(b) shows the Monte Carlo results (1000 points) for the TC of I<sub>ref</sub>, which comes out to have a mean of 337.17ppm/°C and a standard deviation of 15.16ppm/°C. These results prove that we can avoid trimming in this architecture, considering the achieved nominal values and accuracies for both voltage and current reference. The layout of the proposed voltage/current reference takes an area of 0.0112mm<sup>2</sup> as illustrated in Fig. 3.8.

Figure 3.3: (a)  $V_{ref} \& I_{ref}$  vs Temperature (b) Supply sensitivity of  $V_{ref} \& I_{ref}$

Figure 3.4: Start-up time of (a)  $V_{ref}$  and (b)  $I_{ref}$

Figure 3.5: Monte Carlo results for (a)  $V_{\it ref}$  (b)  $I_{\it ref}$  value at 27°C

Figure 3.6:  $\pm 3\sigma$  variation of (a) V<sub>ref</sub> (b) I<sub>ref</sub>

Figure 3.7: Monte Carlo results for TC of (a)  $V_{ref}$  (b)  $I_{ref}$

|                                            | This work   | [31]       | [32]       | [33]        | [19]     | [18]      | [26]      | [24]     |

|--------------------------------------------|-------------|------------|------------|-------------|----------|-----------|-----------|----------|

| Technology(nm)                             | 90          | 180        | 180        | 90          | 350      | 180       | 65        | 350      |

| Туре                                       | Vref/Iref   | Vref/Iref  | Vref/Iref  | Vref/Iref   | Vref     | Vref      | Iref      | Iref     |

| $V_{DD}$ (Supply range)                    | 1V-3.5V     | 0.7V-2V    | 2-5V       | 1V-3V       | 1.4V-3V  | 0.8-2.2   | 1.2V-1.5V | 1.3V-3V  |

| Power(nW)                                  | 37          | 28         | 192        | 0.156       | 300      | 360       | 126560    | 88.53    |

| V <sub>ref</sub> (V)/I <sub>ref</sub> (nA) | 0.820/3.23  | 0.368/9.97 | 1.2/51     | 0.534/0.043 | 0.745/-  | 0.489/-   | -/8800    | -/9.95   |

| $\sigma/\mu(\%)$                           | 1.34/1.75   | 0.35/1.6   | 0.17/1.15  | 4.2/2       | 7/-      | 0.5/-     | -/1.4     | -/14.1   |

| Trimming used                              | No          | Yes        | Yes        | Yes         | No       | Yes       | No        | No       |

| Temperature Range(°C)                      | -40 - 100   | -40 - 125  | -45 - 125  | -55 - 100   | -20 - 80 | -30 - 110 | 0 - 100   | -20 - 80 |

| TC (ppm/°C)                                | 62/332      | 43.1/149.8 | 32.7/89    | 22/58       | 7/-      | 6.5/-     | -/276.8   | -/1190   |

| Line Sensitivity (%/V)                     | 0.296/0.414 | 0.027/0.6  | 0.058/1.76 | 0.029/0.059 | 0.002/-  | 0.076/-   | -/4.5     | -/0.046  |

| PSRR (db@DC)                               | -48         | -59        | -46        | -77         | -45      | -75       | -         | -        |

| Area (mm <sup>2</sup> )                    | 0.0112      | 0.055      | 0.063      | 0.00157     | 0.056    | 0.0180    | -         | 0.12     |

| Resistors/Amplifiers/Thin oxide            | Not Used    | Used       | Used       | Used        | Not Used | Not Used  | Used      | Not Used |

| Result Type                                | Simulated   | Measured   | Measured   | Simulated   | Measured | Simulated | Simulated | Measured |

Table 3.1: Performance summary and comparison with the state-of-arts

Table 3.1 summarizes the performance of the proposed voltage/current reference circuit and compares its performance with the state-of-the-art designs. The designs [31, 32, 33] present both voltage/current references in a single circuit. The usage of resistors in the design[31] increases its area to 0.055mm<sup>2</sup>. The design [32] works for a minimum supply of 2V. Design [33] uses thin oxide devices to reduce its power consumption but usage of such devices has increased their process variations ( $\sigma/\mu$ ) to 4.2%/2%. When compared to the voltage reference designs [18] and [19], design [18] works for a high supply voltage > 1.3V, and design [19] consumes power greater than 350nW. Current reference designs [24] and [25] listed in Table 3.1 work for a supply voltage greater than 1V, but design [24] exhibits a high-temperature coefficient of 1190ppm/°C and substantial process variations. Furthermore, all these designs necessitate additional complex trimming circuitry, increasing the overall design area. Although the design [25] doesn't require trimming, it takes a huge power of 126.56 $\mu$ W and doesn't work for negative temperatures. The presented design in this thesis eliminates the need for external trimming circuitry while maintaining other specifications, with process variations ( $\sigma/\mu$ ) of 1.34%/1.75% that are comparable to post-trim results of state-of-the-art designs. To the best of the author's knowledge, this thesis presents a first and novel all-in-one trim-free, all-MOSFET  $V_{ref}/I_{ref}$  architecture.

## 3.4 Conclusion

This thesis presents a novel trim-free, low process variation, ultra-low power all CMOS voltage/current reference without using high-valued resistances, BJTs, or NVT devices. As it does not incorporate sub-threshold leakage behavior, it works over a wide temperature range of -40 to 100°C. The circuit consumes 37nW and works from a minimum supply of 1V over the wide supply range of 1V - 3.5V. The proposed architecture is trim-free, as the variations of the temperature coefficients and the nominal values of both the voltage and current references are insignificant. All the above competitive specifications make it a desirable choice for various ultra-low power wearables and IoT applications.

Figure 3.8: Layout of proposed voltage/current reference

## Chapter 4

## A 0.8-V, 593-pA Trim-free Duty-cycled All CMOS Current Reference for Ultra-Low Power IoT Applications

## 4.1 Introduction

The increasing need for wireless sensor networks (WSNs) and the Internet of Things (IoT) has led to a significant emphasis on the design of sub-threshold circuits that exhibit ultra-low power consumption [36]. Current references being essential components of any IoT system should also scale their power to satisfy the new requirements and make it ideal for power-constrained applications. Duty cycling has proven to be an effective technique in various applications, including wireless sensor networks, batterypowered devices, and Internet of Things (IoT) systems. By intelligently managing power consumption, duty cycling enables longer battery life, reduced energy costs, and improved overall system efficiency. Traditional current reference circuits often require meticulous manual calibration to compensate for process variations, temperature fluctuations, and aging effects. These calibration procedures not only add complexity to the manufacturing process but also contribute to increased manufacturing costs. By eliminating the need for manual calibration and offering enhanced accuracy and stability, the Trim-free architecture holds tremendous potential to improve the performance, reliability, and power efficiency of IoT devices.

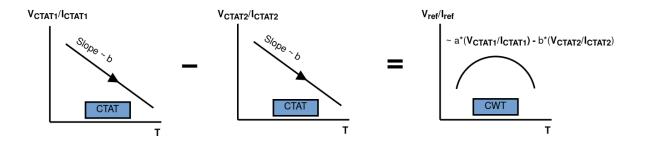

Figure 4.1: Concept of Proposed Current reference

Figure 4.2: Complete schematic of proposed current reference

The conventional current references [37, 38, 39] typically employ resistor-based configuration to generate a stable reference current. However, a resistor-based design shows a significant trade-off arising in terms of area requirements as they demand a considerably larger area to scale the power consumption within the range of nW and pW. To mitigate this issue, [40] replaces the resistor in the beta-multiplier with a MOSFET in deep triode to achieve power consumption in nW but at the cost of high process variation and large voltage supply (Min. supply = 1.2 V). [41] proposed a current reference with a lower supply and nW power consumption. However, the process variation ( $\sigma/\mu$ ) of the design is > 10%. [42, 43, 44] proposed a trim-free current references without using resistors and operational

amplifiers. However, the architecture of those trim-free circuits requires a minimum supply of 1.4 V. Design [45] improves the process variation of the current reference with a process tracking circuit but the power consumption, line sensitivity, and temperature range make it unsuitable for low-power IoT applications. Design [46] proposed a current reference with low power and excellent line sensitivity but the minimum supply voltage is > 1.2 V. Design [47] proposed a low-supply, low-power sub-nA current reference but a Temperature Coefficient(TC) of >500 ppm/°C and requires an external complex trimming circuit to improve process variation of the design. [48] proposed a pico-watt resistor-less current reference with low line sensitivity at the cost of high-temperature variation (780 ppm/°C) and supply voltage (Min. supply > 1.2 V). [49, 50] proposed current references using tunneling currents, although these references require lower area, the susceptibility of tunneling currents to  $t_{ox}$  variations [51] ( > 600% across process corners) necessitates extensive trimming and increases the cost.

This thesis presents a sub-1V, sub-nA, duty-cycled, All-MOSFETs trim-free current reference without using resistors and amplifiers by applying a CTAT (complementary-to-absolute-temperature) voltage at the gate of the MOSFET ( $M_{ref}$ ) and PTAT (proportional-to-absolute-temperature) voltage at the drain of  $M_{ref}$  as shown in Fig. 4.1. The subsequent sections of this thesis are organized as follows: Section 4.2 provides a comprehensive description of the design and analysis of the proposed current reference. In Section 4.3, the simulated results are presented and conclusions are drawn in Section 4.4.

## 4.2 Design and analysis of the proposed Current reference

The schematic of the proposed design, as illustrated in Fig. 4.2, comprises several key components. These include a current source bias circuit, a CTAT generator, and a sub-threshold triode-resistor-based beta-multiplier. The biasing circuit creates a current by employing a self-biasing beta-multiplier circuit with a triode resistor [52]. This bias current is used to establish the CTAT voltage. The CTAT generator, based on a differential pair configuration, produces an output voltage that works as the gate-source voltage of the MOSFET  $M_{ref}$ . This MOSFET operates in the sub-threshold triode region, resulting in low power consumption. Concurrently, a PTAT voltage, crucial for temperature compensation, needs to be applied as the drain-source voltage of MOSFET  $M_{ref}$ . This is achieved with the assistance of the beta-multiplier, ensuring that the generated current, denoted as  $I_{ref}$ , remains independent of variations in temperature, process, and voltage. By integrating these components and leveraging their functionalities, the proposed design aims to achieve robust and precise performance across different operating conditions, making it suitable for a wide range of applications.

#### 4.2.1 Temperature Compensation of Proposed Current Reference

As shown in Fig. 4.2, the current  $I_{ref}$  is determined by the MOS resistor  $M_{ref}$ , where the gate-source voltage is  $V_{GS,M_{ref}}$  and the drain-source voltage is  $V_{DS,M_{ref}}$ . When the MOSFET  $M_{ref}$  operates in the sub-threshold triode region, characterized by  $V_{GS} < V_{TH}$  and  $V_{DS} < V_T$ , the current through  $M_{ref}$

can be described by (4.1) as:

$$I_{ref} = K_n \frac{W}{L} \left(\eta - 1\right) V_T^2 \exp\left(\frac{V_{GS} - V_{TH}}{\eta V_T}\right) \left(1 - \exp\frac{-V_{DS}}{V_T}\right)$$

(4.1)

where  $K_n = \mu_n C_{ox}$ ,  $V_{TH}$  represents the threshold voltage of the transistor,  $V_T$  is the thermal voltage and  $\eta$  is the sub-threshold slope constant. To simplify (1), we can approximate the term  $\left(1 - \exp\left(\frac{-V_{DS}}{V_T}\right)\right)$  as  $\frac{V_{DS}}{V_T}$ , leveraging the binomial expansion of the exponential function for cases where  $\frac{V_{DS}}{V_T}$  is less than 1. This approximation allows us to rewrite (4.1) as (4.2) i.e.

$$I_{ref} = K_n \frac{W}{L} \left(\eta - 1\right) V_T \exp\left(\frac{V_{GS} - V_{TH}}{\eta V_T}\right) V_{DS}$$

$$(4.2)$$

Achieving temperature-independent current  $\left(\frac{\partial I_{ref}}{\partial T}=0\right)$  requires accounting for the variations in  $\mu_n$ ,  $V_T$  and  $V_{TH}$  with temperature. Thus, to ensure a temperature-independent current from the  $M_{ref}$ ,  $V_{GS,M_{ref}}$  and  $V_{DS,M_{ref}}$  are designed as the functions of temperature. Temperature compensation is a crucial aspect of current reference design to ensure accurate and stable performance. In our design, we incorporate a CTAT generator and a PTAT generator to achieve temperature compensation. The CTAT generator connects a CTAT voltage to the gate of MOSFET  $M_{ref}$ . It consists of an NMOS differential pair and a current mirror, which is biased using a current source bias circuit ( $I_{bias}$ ). When the MOSFETs operate in the sub-threshold region, the output voltage of the CTAT generator i.e.  $V_{GS,M_{ref}}$  can be expressed using (4.13)

$$V_{GS,M_{ref}} = V_{GG} + V_1$$

=  $\eta V_T \ln \left( \frac{K_{M14} K_{M17}}{K_{M13} K_{M18}} \right) + V_{th} + \eta V_T \ln \left( \frac{I_{bias}}{I_0} \right)$

=  $V_{TH} + \eta V_T \ln \left( \frac{K_{M14} K_{M17} I_{bias}}{K_{M13} K_{M18} I_0} \right)$  (4.3)

Where  $I_0 = K_n(\eta - 1)V_T^2$ ,  $V_{GG}$  is the gate-to-gate voltage of the CTAT generator, and  $V_1$  is the output voltage of the current source bias circuit which acts as an input to the CTAT generator. In the proposed circuit, PTAT voltage is generated at the drain of  $M_{ref}$  using a supply-independent beta-multiplier circuit. The drain-to-source voltage of MOSFET  $M_{ref}$  serves as the PTAT voltage. The  $V_{DS}$  of  $M_{ref}$  can be expressed as :

$$V_{DS,M_{ref}} = V_{GS,M21} - V_{GS,M22}$$

=  $\eta V_T \ln \left( \frac{W_{22}L_{21}}{W_{21}L_{22}} \right)$

=  $\eta V_T \ln (n)$  (4.4)

where  $\frac{W_{22}}{L_{22}} = n \frac{W_{21}}{L_{21}}$  and n > 1, to make the  $V_{DS}$  of  $M_{ref}$  a PTAT voltage. By substituting the expressions for  $V_{GS,M_{ref}}$ , and  $V_{DS,M_{ref}}$  from (3) and (4) into (2), we obtain the expression for  $I_{ref}$  in terms of temperature.

$$I_{ref} = K_n \frac{W}{L} \eta(\eta - 1) V_T^2 \ln(n) \left(\frac{K_{M14} K_{M17} I_{bias}}{K_{M13} K_{M18} K_n (\eta - 1) V_T^2}\right)$$

(4.5)

$$I_{ref} = \eta \frac{W}{L} \ln(n) \left( \frac{K_{M14} K_{M17} I_{bias}}{K_{M13} K_{M18}} \right)$$

(4.6)

(4.5) provides the derived expression, taking into account various transistor parameters and the current source bias circuit. Simplifying (4.5), we arrive at (4.6), which reveals that the terms within the equation are temperature-independent. Consequently, we can conclude that the generated current reference exhibits temperature invariance, ensuring stable operation across a wide temperature range of -40 to 100°C.

#### 4.2.2 Process variation of the proposed current reference

To study the effect of process variation on the current reference, one needs to check the process variant terms present in the equations  $I_{ref}$ . (4.2) highlights the significance of the threshold voltage, which plays a key role in process variation [53]. The equation includes  $V_{GS,M_{ref}}$ , which can be expressed as  $V_{GS,M_{ref}} = V_{TH} + \eta V_T \ln \left(\frac{K_{M14}K_{M17}I_{bias}}{K_{M13}K_{M18}I_0}\right)$ . Substituting the value of  $V_{GS,M_{ref}}$  into (4.2) we get :

$$I_{ref} = K_n \frac{W}{L} \eta(\eta - 1) V_T^2 \exp\left(\frac{V_{TH} + \eta V_T \ln(\frac{K_{M14}K_{M17}I_{bias}}{K_{M13}K_{M18}I_0}) - V_{TH}}{\eta V_T}\right)$$

(4.7)

In (4.7), there is a cancellation of the  $V_{TH}$  term, leading to an improvement in the process variation of the reference current. Fig. 4.7(b) depicts the value of  $V_{GS,M_{ref}} - V_{TH,M_{ref}}$  at different process corners, demonstrating minimal variation. By examining the equations and considering the cancellation of the  $V_{TH}$  term, we can say that the reference current is less susceptible to process variations.

#### 4.2.3 Improvement in Line Sensitivity of the Proposed Current Reference

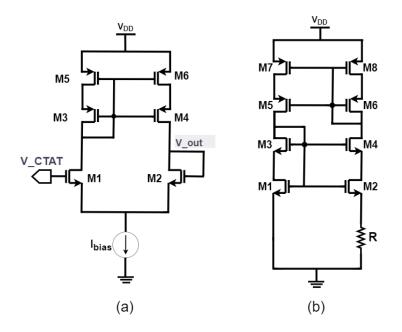

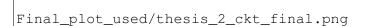

Figure 4.3: (a) Concept of subtracting two current references (b) Simulation of Subtracted current references

In the proposed design, we have implemented a technique to enhance the line sensitivity of the reference current [54]. The technique involves generating a reference current with improved line sensitivity by subtracting two temperature-compensated current references: one with normal line sensitivity  $(I_{ref1})$  and the other with poor line sensitivity  $(I_{ref2})$  as shown in Fig. 4.3(a). These current references are derived from beta-multiplier structures. The equation for the reference current with improved line sensitivity is given as

$$I_{ref} = I_{ref1} - p * I_{ref2} \tag{4.8}$$

where p represents the coefficient of subtraction. To achieve this, we intentionally designed  $I_{ref2}$  to have a greater variation with supply voltage  $(V_{DD})$  compared to  $I_{ref1}$ . This is accomplished by reducing the lengths of the NMOS transistors and modifying the current mirror architecture. Fig. 4.3(b) illustrates the variations of  $I_{ref1}$ ,  $I_{ref2}$ , and  $I_{ref}$  with respect to the supply voltage  $(V_{DD})$ . Based on the data analysis, we can approximate the equations for  $I_{ref1}$ ,  $I_{ref2}$ , and  $I_{ref}$  in terms of  $V_{DD}$  as

$$I_{ref1} = A * V_{DD} + c_1 \quad and \quad I_{ref2} = B * V_{DD} + c_2$$

$$(4.9)$$

$$I_{ref} = (A - p * B) * V_{DD} + (c_1 - p * c_2)$$

(4.10)

Where A and B are the slopes of  $I_{ref1}$  and  $I_{ref2}$  respectively. To ensure the desired line sensitivity of the reference current, the value of p is chosen such that the difference between A and p \* B approaches zero. Since the slope of B is greater than that of A, selecting p < 1 meets our requirement but a small value of p may increase the offset that may occur during the mirroring of  $I_{ref2}$  due to the absence of a cascode structure in the beta-multiplier. By considering the aforementioned suggestions, we can enhance the circuit's performance, particularly its line sensitivity, beyond what is achievable with a conventional cascode beta-multiplier-based current reference. This improvement is attained by completely eliminating the first-order dependence on the supply voltage through the appropriate selection of the coefficient p. These advancements signify significant progress in performance, offering enhanced stability and reduced sensitivity to changes in the supply voltage.

|                                   | This work   | [43]      | [44]         | [42]        | [40]        | [47]      | [48]     | [46]      |

|-----------------------------------|-------------|-----------|--------------|-------------|-------------|-----------|----------|-----------|

| Technology (nm)                   | 90          | 180       | 65           | 180         | 180         | 180       | 180      | 350       |

| $V_{DD}$ (Supply range)           | 0.8 - 2.5 V | 1 - 2 V   | 1.25 - 1.4 V | 1.5 - 2.4 V | 1.2 - 1.8 V | 0.7 - 2 V | 1.2 - 4V | 1.3 - 3 V |

| Power(nW)                         | 3.3         | 1231      | 550          | 1.02        | 670         | 1.06      | 0.023    | 88.53     |

| I <sub>ref</sub> (nA)             | 0.593       | 142.5     | 104.2        | 35          | 92.3        | 0.192     | 0.020    | 9.95      |

| Process Variation $(3\sigma/\mu)$ | 0.75%       | 9.4%      | 4%           | 4.3%        | 18.4%       | -         | -        | 42%       |

| Trimming used                     | No          | No        | No           | No          | No          | Yes       | Yes      | Yes       |

| Temperature Range (°C)            | -40 - 100   | -40 - 85  | -45 - 85     | -40 - 120   | -40 - 85    | -20 - 80  | 0 - 80   | -20 - 80  |

| TC (ppm/°C)                       | 378         | 40        | 48           | 282         | 179.9       | 546       | 780      | 1190      |

| Line Sensitivity (%/V)            | 0.198       | 1.45      | 1.9          | 3           | 7.5         | 0.51      | 0.58     | 0.046     |

| Area (mm <sup>2</sup> )           | 0.074       | 0.02      | 0.0031       | 0.017       | 0.0007      | -         | 0.0484   | 0.12      |

| Resistors/Amplifiers              | Not Used    | Not Used  | Not Used     | Not Used    | Not Used    | Not Used  | Used     | Not Used  |

| Result Type                       | Simulated   | Simulated | Simulated    | Measured    | Measured    | Simulated | Measured | Measured  |

Table 4.1: Performance summary and comparison with the state of arts

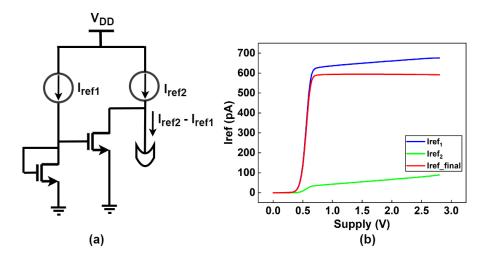

#### 4.2.4 Duty-cycling of Proposed Current Reference

As shown in Fig. 4.4, the CTAT generator is designed to operate in a duty-cycled manner in order to conserve power. Without duty-cycling, the overall power consumption amounts to 52.8 nW, with the CTAT generator accounting for approximately 95% of this total. However, by implementing a duty-cycling scheme of 1.33% on the CTAT generator, a power saving of around 94% is achieved. In addition to employing this duty-cycling technique, a start-up circuit is needed for the bias circuit beta-multiplier to guarantee a correct output when duty-cycled switches are ON [55] whereas, always ON current reference core beta-multipliers require a single pulse startup circuit to generate the reference current.

Figure 4.4: Duty-cycling schematic

Figure 4.5: The timing waveform of the current reference

The timing diagram for the current reference operation is illustrated in Fig. 4.5. In the background, a real-time clock continuously operates to provide a low frequency, driven by a low-frequency oscillator [56]. Additionally, a duty-cycled clock with an active time of 1.33% is used to provide the necessary clock signal ( $Clock_{DC}$ ) to the switch (S1, S2). As shown in Fig. 4.5 a startup pulse is generated by