# **Algorithm Driven Transistor sizing based Power-Timing Optimization Methodology for CMOS Digital Circuits**

Thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science in Electronics and Communication Engineering

Hema Sai Kalluru 201531221

kalluru.hemasai@research.iiit.ac.in

International Institute of Information Technology Hyderabad - 500 032, INDIA July 2023

Copyright © Hema Sai Kalluru, 2022 All Rights Reserved

# International Institute of Information Technology Hyderabad, India

# **CERTIFICATE**

| It is certified that the work contained in this thesis, tit based Power-Timing Optimization Methodology & Kalluru, has been carried out under my supervision a | for CMOS Digital Circuits" by Hema Sai |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|                                                                                                                                                                |                                        |

|                                                                                                                                                                |                                        |

| ——————————————————————————————————————                                                                                                                         | Advisor: Dr. Zia Abbas                 |

#### Acknowledgments

Foremost, I would like to express my sincere gratitude to my advisor, Dr Zia Abbas, for the continuous support in academics and research, for his patience, motivation and invaluable guidance. He has taught me the methodology to carry out the research and to present the work as clearly as possible. He taught me to be passionate at work and compassionate with people. It was a great privilege and honor to work and study under his guidance.

I would like to thank all the people who have supported me and motivated me throughout my journey at IIITH. A special thanks to my friends from IIIT family, Harshini, Sailaja, Bhavya, Harish, Harsha, Ashfakh, Shirisha, Preetham and others, who have kept my spirits alive throughout this beautiful journey and for making my college life more cherish-able. I would like to acknowledge and thank everyone in CVEST lab for helping me and and for taking part in brain storming the ideas throughout this journey. I extend my token of gratitude to all the Distinguished Faculty in the college without whose cooperation and support, this journey would not have been possible.

I can never thank my parents enough for their love, prayers, care and sacrifices for educating me and preparing me for my future. I am thankful to have the blessings of my grand-parents and constant support of my friends.

#### **Abstract**

During the past few decades, the semiconductor VLSI industry has distinguished itself both by the rapid pace of performance improvements, and by a steady path of constantly shrinking device geometries. MOSFETs upon downsizing, have met the world's growing needs for electronic devices like computing, communication, entertainment, automotive, and other applications with steady improvements in cost, speed, and area. But the device density has led to increased power consumption. Hence, Leakage, along with propagation Delay are the key metrics to evaluate the performance of any digital circuit. In nano-scale technologies(<45nm), static power occupies a significant share in the total power budget thereby prioritizing the need for leakage reduction techniques.

Performance optimization of CMOS based circuits gains more significance for nano scale technology nodes. Variations in operating parameters such as supply voltage, temperature etc. have profound effects on power-delays specifications. The non-homogeneity in process parameters at such scaled technologies hampers the yield of the final designs. Performance degradation over time is another important factor determining the lifetime and reliability of an IC. In this work we develop a framework of algorithms to optimize digital circuits for low power and high performance applications. A wide range of analysis such as sensitivity of the circuit, correlation between parameters etc has been performed to understand the functioning in response to transistor sizing of digital cells.

The first stage of this work aims to optimize basic digital cells through transistor sizing using the proposed optimization algorithms like Pareto Harris Hawk optimization algorithm, Glowworm Swarm optimization algorithm, Strength Pareto evolutionary algorithm-II and Neighbourhood Cultivation Genetic algorithm. The resultant system design becomes robust to withstand fluctuations caused by process, aging and operating parameters apart from providing highly improved leakage-delay performances.

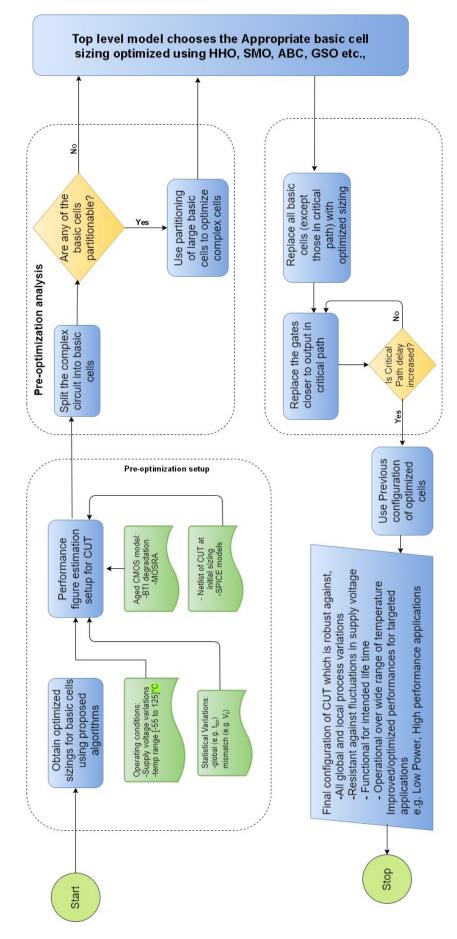

The second stage of this work involves optimization complex circuits. We have proposed a framework to optimize the complex circuits by selectively replacing the basic cells with the optimized sizing. The proposed framework deconstructs a given circuit into its constituent basic cells. It does a wide range of analysis such as sensitivity, the correlation between process parameters, load analysis, screening of insignificant parameters, and mismatch analysis to generate robust sizing. The algorithms generate sizing that can be used at multiple instances across different circuits. Thus the total number of design variables remains within a limit even when the cell count increases across circuits.

The proposed framework then reconstructs the circuit with these optimized cells to improve the power-delay front. While replacing the nominal with the optimized sizing for each cell, the tool identifies the load it has to drive, the path (critical/ non-critical) it is present in and its driver modules in the path. The basic cells are selectively replaced with the optimized sizing using the proposed techniques: Backward traversal replacement technique and Partitioning large basic cells. Results have shown a substantial reduction in leakage power and propagation delays in addition to minimizing human effort

# **Contents**

| Ch | apter                      |                                                              | Page         |

|----|----------------------------|--------------------------------------------------------------|--------------|

| 1  | Intro<br>1.1<br>1.2<br>1.3 | Motivation                                                   | . 1          |

|    | 1.4                        | Thesis Outline                                               | . 3          |

| 2  | Impa<br>2.1                | act of Technology Scaling On Performance of Digital Circuits | . 5          |

|    | 2.2                        | Power Dissipation in CMOS Digital Circuits                   | . 6          |

|    | 2.3                        | Sources of Power consumption                                 | . 7          |

|    |                            | 2.3.2 Static Power dissipation                               | . 7          |

| 3  | Impa                       | 2.3.4 Trends in Power Dissipation                            |              |

|    | 3.1<br>3.2<br>3.3          | Introduction                                                 | . 9          |

|    | 3.4                        | 3.3.1 Supply Voltage                                         | . 10<br>. 12 |

|    | 3.5<br>3.6                 | PVTA range considered for the optimization                   | . 13         |

|    | 3.7                        | Summary                                                      |              |

| 4  | Circ 4.1 4.2 4.3           | uit Analysis                                                 | . 18<br>. 18 |

|    | 4.4                        | Mismatch Analysis                                            |              |

| CONTERNIE | •   |

|-----------|-----|

| CONTENTS  | 1V  |

| CONTLINIS | IA. |

|           |     |

|   | 4.5    | Correlation                                                                    | 2        |

|---|--------|--------------------------------------------------------------------------------|----------|

| 5 | Prop   | osed Algorithm methodology using Transistor sizing to optimize performances of |          |

|   | CMC    | OS digital circuits                                                            | 5        |

|   | 5.1    | Introduction                                                                   | 5        |

|   | 5.2    | Pareto Harris Hawk optimization algorithm                                      | 5        |

|   |        | 5.2.1 Case1:                                                                   | 7        |

|   |        | 5.2.2 Case2:                                                                   | 3        |

|   |        | 5.2.3 Case3:                                                                   |          |

|   |        | 5.2.4 Case4:                                                                   |          |

|   | 5.3    | Neighbourhood Cultivation Genetic Algorithm                                    |          |

|   | 5.4    | Strength Pareto evolutionary algorithm - II (SPEA-II)                          |          |

|   | 5.5    | Glowworm swarm optimization algorithm                                          |          |

|   | 5.6    | Implementation                                                                 |          |

|   | 5.0    |                                                                                | ,        |

| 6 | Top 1  | level framework for Complex circuit optimization                               | )        |

|   | 6.1    | Introduction                                                                   | )        |

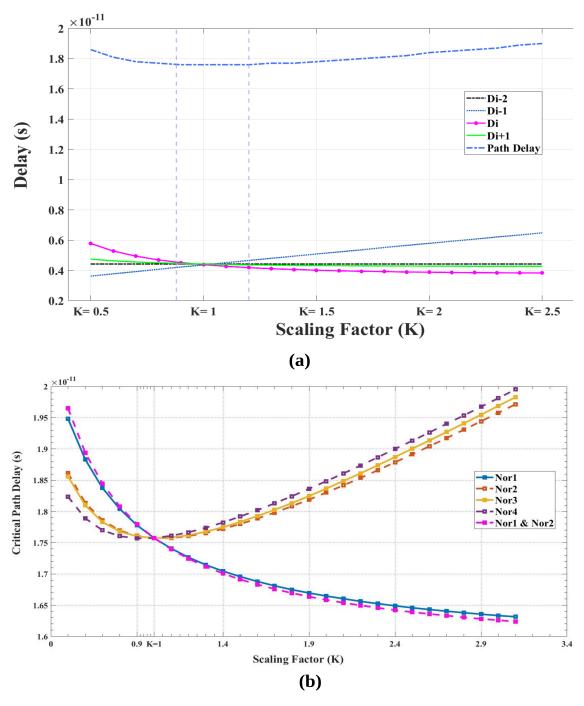

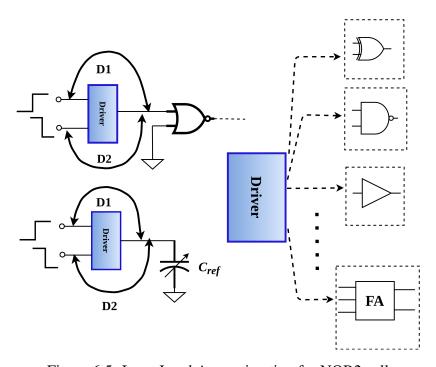

|   | 6.2    | Replacing the basic cells                                                      | )        |

|   | 6.3    | Effect of cell resizing on Delay                                               | 2        |

|   |        | 6.3.1 Load analysis based optimization                                         | 1        |

|   | 6.4    | Complex circuit optimization                                                   | 1        |

|   |        | 6.4.1 Backward Traversal Replacement                                           | 7        |

|   |        | 6.4.2 Partitioning Large Basic cells                                           | )        |

|   |        | 6.4.3 Top level model for complex circuits                                     | )        |

| 7 | A Itas | rnative Approach: Case: polar decoders                                         | <b>S</b> |

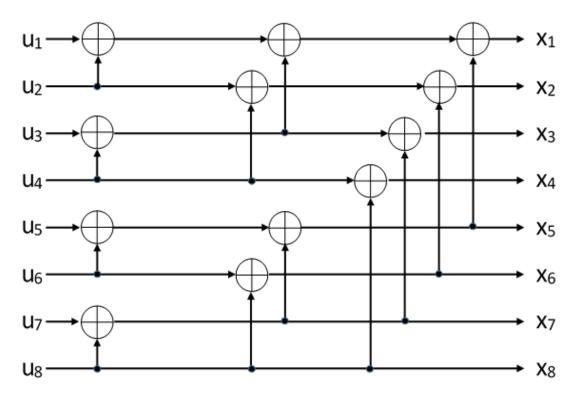

| , | 7.1    | Introduction                                                                   |          |

|   |        |                                                                                |          |

|   | 7.2    | Polar decoders                                                                 |          |

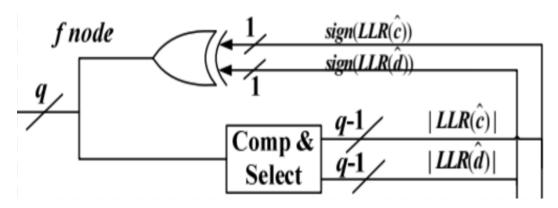

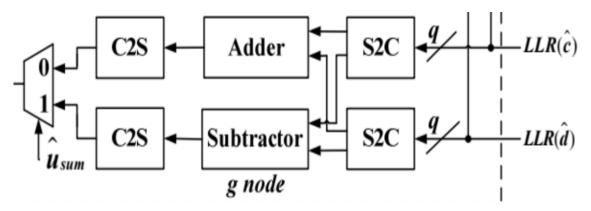

|   | 7.3    | Performance Parameters in Polar decoders                                       |          |

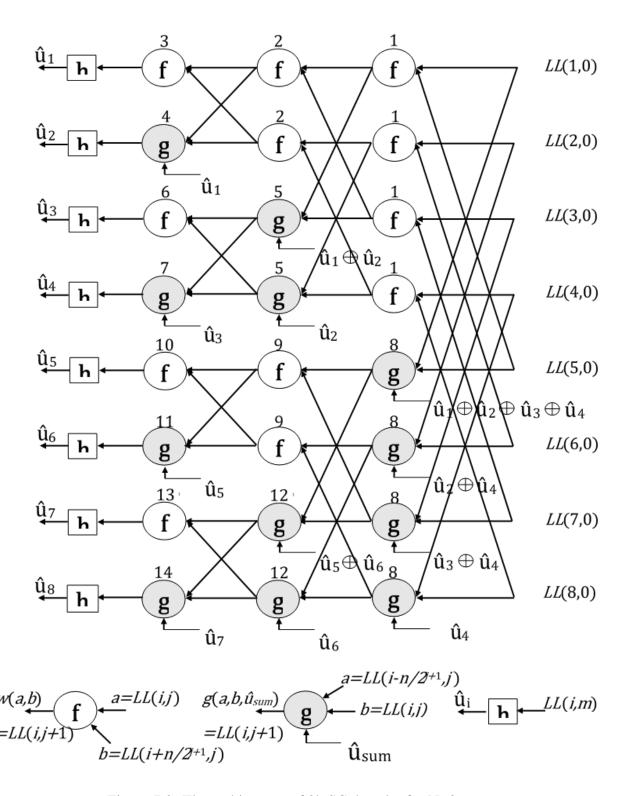

|   | 7.4    | 2b SC Polar decoder Architecture                                               |          |

|   | 7.5    | Background and the latencies of 2b SC architectures                            |          |

|   | 7.6    | Proposed novel 2b SC Polar decoder architecture                                |          |

|   |        | 7.6.1 Iterative Decomposition                                                  |          |

|   |        | 7.6.2 Proposed 2b SC Polar decoder design                                      |          |

|   | 7.7    | Results                                                                        |          |

|   | 7.8    | Conclusion                                                                     | 7        |

| 8 | Conc   | clusion and Future Work                                                        | 3        |

# **List of Figures**

| Figure |                                                                                                             | Page |

|--------|-------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Illustration of Moore's law: The number of transistors in different microchips against production years [1] | . 2  |

| 2.1    | Dynamic and Static power consumption trends based on ITRS                                                   | . 8  |

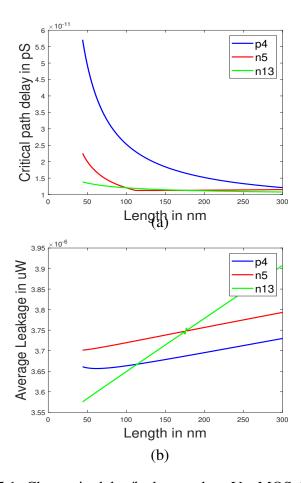

| 3.1    | Impact of Process variations on (a) Critical Path Delay and (b) Average Leakage for a Full adder            | . 11 |

| 3.2    | Impact of (a) Supply voltage on Leakage, (b) Temperature on critical path delay of 1b-Full Adder            | . 12 |

| 3.3    | The change of gate delay due to NBTI at D=t [2]                                                             |      |

| 3.4    | Impact of Process, Operating and Aging variations on critical path delay of Full adder at nominal sizing    |      |

| 3.5    | Impact of Process variations on (a) Critical Path Delay and (b) Average Leakage for a Full adder            | . 16 |

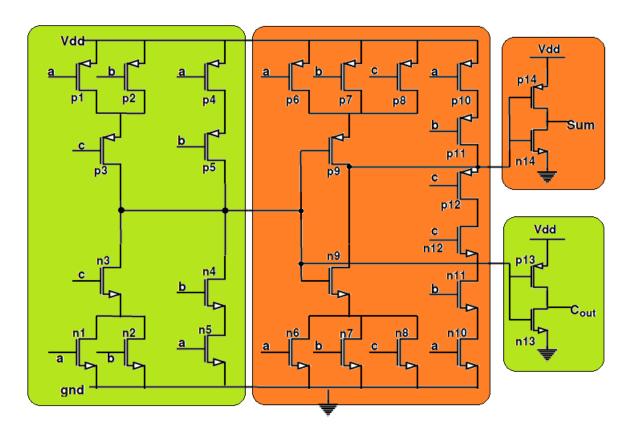

| 4.1    | CMOS 28T Full Adder Cell                                                                                    | . 19 |

| 4.2    | Sensitivity of design parameters for 28T Full adder                                                         | . 20 |

| 4.3    | Correlation of aging and toxp                                                                               |      |

| 4.4    | Correlation between few Process Parameters                                                                  | . 23 |

| 5.1    | Change in delay/leakage values Vs. MOS dimensions                                                           | . 26 |

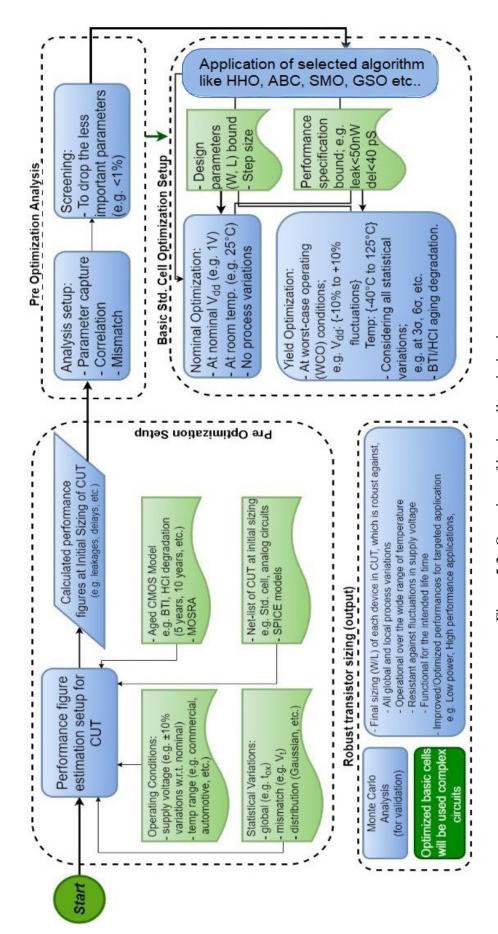

| 5.2    | Overview of basic cell optimization                                                                         | . 36 |

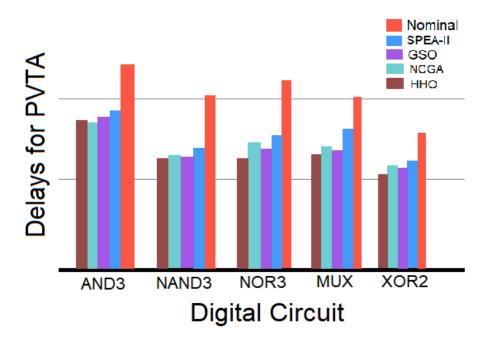

| 5.3    | Delay optimization with PVTA variations for Basic cells                                                     | . 39 |

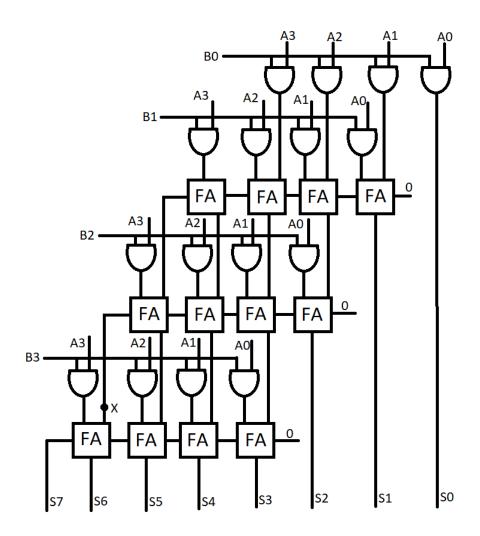

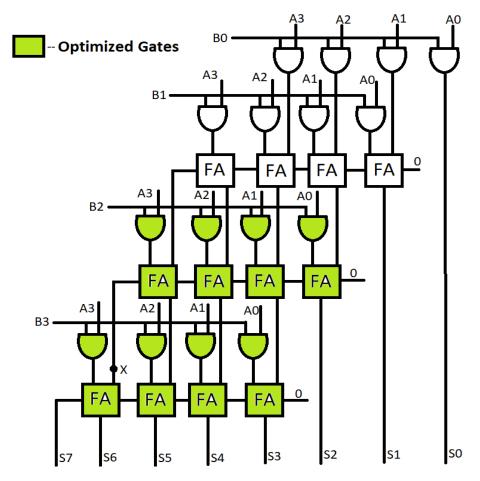

| 6.1    | 4 bit Multiplier                                                                                            | . 41 |

| 6.2    | Logic path with re-sized cell                                                                               | . 42 |

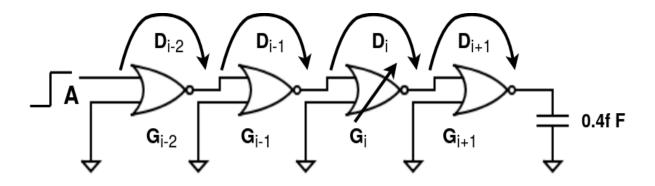

| 6.3    | Impacts of (a) Individual and Group of Gate (b) Resizing on Gate and Path Delays                            |      |

| 6.4    | Load based Optimization                                                                                     |      |

| 6.5    | Input Load Approximation for NOR2 cell                                                                      | _    |

| 6.6    | 4 bit Multiplier                                                                                            |      |

| 6.7    | Partitioned CMOS 28T Full Adder Cell                                                                        |      |

|        |                                                                                                             |      |

| LIST OF FIGURES | xi |

|-----------------|----|

|                 |    |

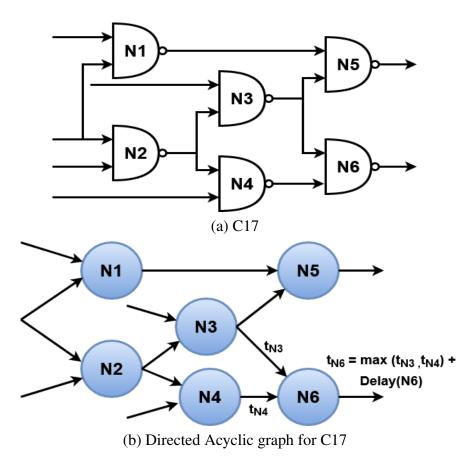

| 6.8<br>6.9 | Representation of C17 as Directed Acyclic graph                             |

|------------|-----------------------------------------------------------------------------|

| 7.1        | Polar Encoder for N=8                                                       |

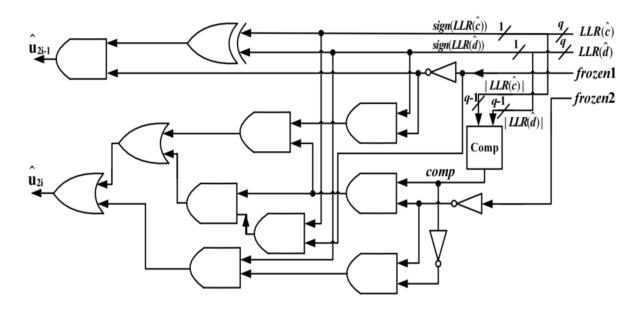

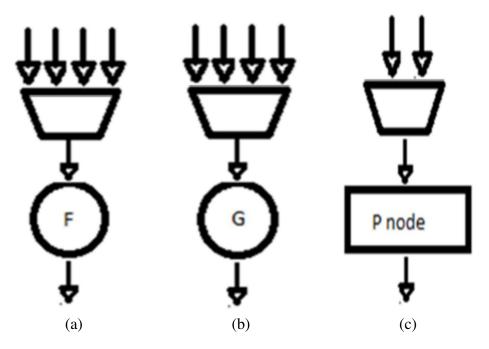

| 7.2        | The architecture of 2b SC decoder for N=8                                   |

| 7.3        | F-Node of a 2b SC Polar decoder                                             |

| 7.4        | G-Node of a 2b SC Polar decoder                                             |

| 7.5        | P-Node of a 2b SC Polar decoder 61                                          |

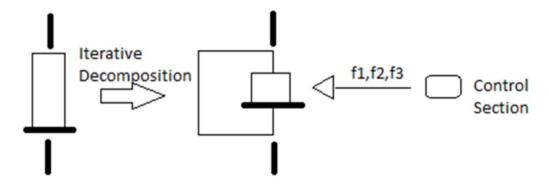

| 7.6        | Iterative decomposition                                                     |

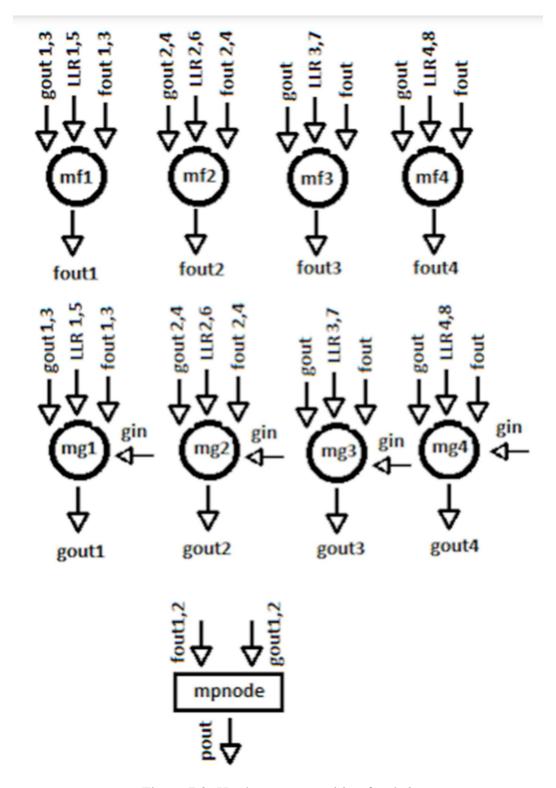

| 7.7        | Hardware composition for d=3                                                |

| 7.8        | Hardware composition for d=3                                                |

| 7.9        | Modified Nodes with multiplexers (a). Modified F node, (b) Modified G node, |

|            | (c) Modified P node                                                         |

# **List of Tables**

| Table      |                                                                               | Page |

|------------|-------------------------------------------------------------------------------|------|

| 3.1        | Process variations considered for 22nm CMOS technology                        | . 14 |

| 4.1        | Process variations considered for 22nm CMOS technology                        | . 24 |

| 5.1<br>5.2 | Initial sizing and bounds of the design Parameters                            | . 34 |

| 3.2        | performance circuits)                                                         | . 35 |

| 5.3        | Robust Sizing obtained for 28T 1-bit Full Adder cell at 22nm technology       | 2.5  |

| 5.4        | node                                                                          | . 37 |

| 5.1        | NOC and PVTA conditions                                                       | . 38 |

| 5.5        | Average Leakage( $\mu W$ ) optimization of Basic cells at 22nm technology for |      |

|            | NOC and PVT conditions                                                        | . 38 |

| 6.1        | Approximate Input Capacitance for Basic Cells                                 | . 46 |

| 6.2        | Critical path delay(ps) optimization of complex circuits using the devel-     |      |

|            | oped model at 22nm technology at NOC and PVTA conditions                      |      |

| 6.3        | Leakage Optimization of Complex Cells for NOC and PVT conditions              | . 54 |

| 6.4        | Comparative study of quantitative improvements in proposed work to ex-        |      |

|            | isting works                                                                  | . 55 |

| 7.1        | Comparative study of quantitative improvements in proposed work to ex-        |      |

|            | isting works                                                                  | . 66 |

| 7.2        | Comparative study of quantitative improvements in proposed work to ex-        |      |

|            | isting works                                                                  | . 67 |

#### Chapter 1

#### Introduction

#### 1.1 Motivation

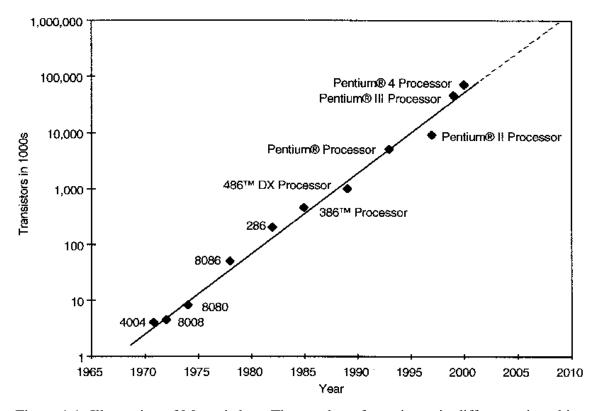

Since the invention of the first Metal Oxide Semiconductor Field Effect Transistors (MOSFET), it has become the basic building block in digital circuit applications such as microprocessors and memories, resulting in low cost, high performance circuits having a high functional density. In 1965, Gordan Moore, the co-founder of Intel made an observation that the number of transistors incorporated in a chip will approximately double every 18 months or so[3]. Since 1975, this prediction, termed as Moore's law has been driving the industry towards long-term planning and set targets in research and development as shown in Figure 1.1.

The last few decades have evidenced tremendous improvements in the power density reduction while keeping and even increasing the device performance as a result of downsizing at every new technology node. However, several unintended consequences have undermined the benefits obtained from the advances in technology. Firstly, a drastic increase in power dissipation with scaling technology nodes, secondly, the growing impact of process variations in fabrication, worsening the power dissipation[4].

#### 1.2 Problem Statement

Continuous miniaturization of complementary metal-oxide-semiconductor (CMOS) technologies has dramatically increased the speed, power efficiency and integration of electronic systems. Moore's law continues to predict the scaling and levels of integration fairly well and the rate of scaling even outperforms the prediction in recent years.

However, this down-scaling is accompanied by increased process variability, in turn, an enormous increase in leakage power. In addition, fluctuations in operating parameters (e.g.

supply voltage and temperature) always significantly deviate the circuit performance from their expected functioning. Moreover, such high-performance circuits are facing a serious threat by aging degradation effects such as Bias Temperature Instability (BTI), which degrade the circuit performance over time. Therefore, circuit optimization for high yield has become a crucial and complex task in IC design. In fact, a high degree of reliability and then the high yield is achievable only if the devices in the circuit are cooperatively invariant against the process and operating variations in conjunction with aging degradation effects.

Figure 1.1: Illustration of Moore's law: The number of transistors in different microchips against production years [1]

#### 1.3 Thesis Contribution

This thesis is mainly focused on optimizing the leakage power and propagation delay in CMOS VLSI circuits using Algorithms, to ensure ingenious working at all process and operating conditions. We mainly propose 4 optimization algorithms in this work to obtain the transistor sizing with optimized device performance. The main contributions of this research can be summarized as follows:

- We have performed Circuit Analysis to analyse the response of the circuit on changing various design parameters, local and global process parameters and correlation between process parameters

- We have proposed Novel Pareto Harris Hawk optimization algorithm, Glowwarm swarm optimization algorithm, Neighbourhood cultivation genetic algorithm and Strength pareto evolutionary algorithm - II (SPEA-II) to solve the optimization problem for basic CMOS digital cells.

- We have proposed two methods for optimizing complex circuits, by selectively replacing the basic cells with the optimized sizing obtained using the algorithms reducing the computational complexity to a great extent. The two methods proposed are: 1) Backward Traversal Replacement and 2) Partitioning large basic cells

- We have proposed a top level model for optimizing the complex circuits, a methodology that deconstructs a given circuit into its constituent basic cells. It does a wide range of analysis such as sensitivity, the correlation between process parameters, load analysis, screening of insignificant parameters, and mismatch analysis to generate robust sizing. The proposed framework then reconstructs the circuit with these optimized cells to improve the power-delay front.

- An alternative method for optimizing the Power dissipation and Area by iterative decomposition technique considering the case of the polar decoders.

#### 1.4 Thesis Outline

The remaining of the thesis is organized as follows:

- In chapter 2, We introduce the topic of Technology scaling, impact of technology scaling on CMOS device performances. We also discuss different types of power dissipation in CMOS devices

- In chapter 3, We discuss the impact of process variations, Operating variations like Supply voltage, Temperature Fluctuations and NBTI aging variations. we have considered  $\pm 3\sigma$  variation in process parameters, temperature range [-55 °C to 125 °C],  $\pm 10\%$  variation in supply voltage i.e. [0.72 to 0.88] and 3 years of NBTI aging.

- In chapter 4, We have performed extensive circuit analysis to understand the behavious of the circuit. In this section, we have performed sensitivity analysis, screening, mismatch analysis and correlation between process parameters.

- In chapter 5, We put forward transistor sizing based optimization technique using algorithms to optimize the leakage power and propagational delay of basic cells. We have proposed pareto Harris Hawk optimization algorithm, Neighbourhood cultivation genetic algorithm, strength pareto optimization algorithm II, and Glowworm swarm optimization algorithm to optimize the basic cells

- In chapter 6, We propose a methodology that deconstructs a given circuit into its constituent basic cells. It does a wide range of analysis such as sensitivity, the correlation between process parameters, load analysis, screening of insignificant parameters, and mismatch analysis to generate robust sizing. The proposed framework then reconstructs the circuit with these optimized cells to improve the power-delay front. While replacing the nominal with the optimized sizing for each cell, the tool identifies the load it has to drive, the path (critical/ non-critical) it is present in and its driver modules in the path. We have proposed two methods to selectively replace the basic cells with optimized sizing in this framework: Backward traversal replacement and Partitioning large basic cells

- In chapter 7, We propose an alternative approach, Iterative decomposition technique to optimize the power dissipated. We have implemented this technique for a particular case of polar decoders.

- In chapter 8, We conclude the thesis and with some future work

### Chapter 2

# Impact of Technology Scaling On Performance of Digital Circuits

#### 2.1 Introduction

The need for affordable, high-performance electronic systems has driven significant research and innovation in the semiconductor industry. In particular, silicon-based technologies have witnessed continuous levels of advancement in order to boost performance and maintain strong economies of scale. The growing market of portable electronic devices demands lesser power dissipation for longer battery life and compact system. Advancement in technology effectively minimizes the leakage current & power and size of the cell. The leakage current in a cell is the dominating factor, which greatly affects power consumption. Optimization of power and delay is a very important issue in low-voltage and low-power applications.

#### 2.2 Power Dissipation in CMOS Digital Circuits

The invention of CMOS digital transistors has significantly reduced power consumption as compared to previous technologies such as transistor-transistor and emitter-coupled logic. The static power i.e., the power dissipated when the circuit is not switching, is almost negligible in the early CMOS transistors. However, the power consumption has increased drastically with the increase in the transistor density and device speed.

Moore's law predicted that the number of transistors in an integrated circuit (IC) would approximately double every 2 years. As predicted, the semiconductor industry advanced through the use of dimensions and voltage scaling to create faster and more densely packed devices entering the ultra large scale integration era (ULSI).

#### 2.2.1 Technology Scaling

There are two methods for obtaining scaling: constant voltage (CV) scaling and constant electric (CE) field scaling. The dimensions of the MOSFET are scaled by a factor 'S' in constant-field scaling, with the goal of preserving the magnitude of the internal electric fields, particularly in device channels. The power supply voltage is also proportional to the size of the device features. Constant electric field scaling is used to improve device reliability and performance. The device dimensions are reduced by a factor of 'S' in constant-voltage scaling while the power supply remains constant[5]. This scaling method is used in CMOS circuits to achieve advanced performance while maintaining transistor-transistor logic compatibility. Power and delay are much more important issues to analyze when we scale down any of the devices under the name of technology.

Constant-field scaling is an excellent framework for device scaling that does not compromise reliability. However, several parameters, such as the thermal voltage and the energy gap of silicon material, cannot be scaled with the reduced voltage and dimensions, posing design challenges. The threshold voltage is another important device parameter that does not scale well. Because a guard margin between the two parameters is required for reliable device operation, this constrains the lower limit of power supply voltage. The scaling of leakage current and the sub-threshold slope are two other parameters that pose difficulties for this method.

Constant-field scaling also results in the greatest reduction in an individual transistor's power-delay product. However, when the minimum feature size is reduced, the power supply voltage must be reduced, making scaling a very difficult task due to the external limitations of the power supply.

One issue with constant voltage scaling is that the electric field in the channel increases as the gate length decreases, resulting in velocity saturation, mobility degradation, increased leakage currents, and lower breakdown voltages, all of which can lead to serious reliability issues such as hot-carrier degradation, electromigration, and oxide breakdown.

# 2.3 Sources of Power consumption

Scaling of CMOS technology improved the speed nevertheless the leakage currents are leftover as an adverse effect. The problem has taken a serious turn as the scaling extends into ultra-deep-submicron (UDSM) region. The total power dissipation in a CMOS circuit can be expressed as the sum of two main components: dynamic power (power dissipated when the circuit is switching.) and static power (power dissipated when the circuit is idle).

#### 2.3.1 Dynamic power dissipation

Dynamic power dissipation is the power consumed when there is any switching activity in a CMOS circuit. It is the power required to charge and discharge all nodes in a CMOS circuit. This power is only dissipated when the input signals in the circuit change. Dynamic power dominates total power dissipation in CMOS circuits. This characteristic is greatly influenced by current processes or deep sub-micron processes (DSM), where the leakage power to dynamic power ratio is increasing[6]. Toatl dynamic power dissipation of a circuit with n nodes is evaluated as follows:

$$P_{dynamic} = V_{dd} \times V_{dd} \times f \times (\sum_{i=1}^{n} \alpha_i \times C_i)$$

where  $\alpha_i$  is the switching activity of node i with capacitance  $C_i$

#### 2.3.2 Static Power dissipation

Since the PMOS and NMOS devices are never on together at the same time in steady-state operation, the static power consumption of static CMOS circuits is assumed to be zero. However, once the gate voltage falls below the threshold voltage, the drain current through the CMOS transistor does not drop to zero. Unfortunately, there is always a leakage current, which is primarily determined by fabrication technology. Historically, static power dissipation has made a relatively insignificant contribution to overall power dissipation and can therefore be neglected. However, with today's technologies, which use lower device threshold voltages to achieve better performance, the percentage of static power dissipation from total power has increased.

#### 2.3.3 Short Circuit Power Dissipation

The dynamic power dissipation assumes the NMOS and PMOS are never simultaneously on i.e., the rise and fall times are zero. In reality, however, such an assumption is incorrect, and input signals have nonzero rise and fall times. As a result, a direct current path exists between Vdd and GND for a brief period of time during input switching, during which the PMOS and

NMOS devices are both conducting. This power component is consumed without contributing to circuit behaviour and is thus deemed redundant.

#### 2.3.4 Trends in Power Dissipation

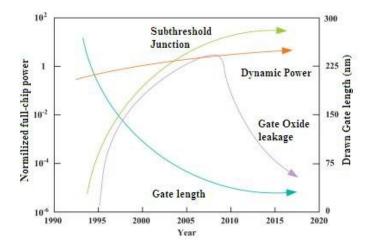

Generally, dynamic power was the dominant component and static power was negligible (Borkar, 1999). But this will totally reverse in the case as the CMOS technology scales down. Static power dissipation is increasing with each new technology node moving towards to smaller nodes. The Figure.2.1 below shows the leakage trends in CMOS devices, where the leakage power dissipation is going beyond Dynamic power dissipation[7].

Figure 2.1: Dynamic and Static power consumption trends based on ITRS

#### Chapter 3

# Impact of PVTA variations on Performance of Digital Circuits

#### 3.1 Introduction

The process and operating variations greatly affect the performances in the CMOS digital circuits particularly in the smaller technology nodes (<90nm). Aging effects degrade the performance of the circuits over time. The objective is to understand the impact of the process, operating and Aging variations and optimize the performances (Leakage power and Propagational delay) of the circuit invariant to these variations.

#### 3.2 Process Variations

Technology scaling in the nanometer era has increased the transistor's susceptibility to process variations. The effects of such variations are having a massive impact on the yield of the integrated circuits and need to be considered early in the design flow. The variations in the device and interconnect parameters such as device threshold voltage  $(V_{th})$ , oxide thickness  $(t_{ox})$ , wire width  $(W_M)$ , and wire height (H) are growing at an alarming rate. Subsequently, the performance of a different die on the same wafer can also vary widely, resulting in a significant parametric yield loss.

As the MOSFET geometries continue to shrink, controlling critical device parameters becomes increasingly difficult, resulting in significant variations in device length, doping concentrations, and oxide thicknesses. These process variations are a significant issue, and the device's operation is no longer deterministic, but rather random. Process variations can be

classified as systematic or random, with systematic variations being deterministic and caused by the structure of a specific gate and its topological environment.

For instance, depending on the density of the surrounding routing, wire thicknesses will polish differently during CPM. Due to lithography limitations and the use of OPC methods, poly gate width has a deterministic dependence on the spacing of neighboring poly lines. Random variations in device length, discrete doping fluctuations, and oxide thickness variations are all unpredictable in nature. The impact of deterministic variations on circuit delay is relatively simple to analyze if accurate models of their dependence on physical topologies and the necessary layout information are available at the time of analysis.

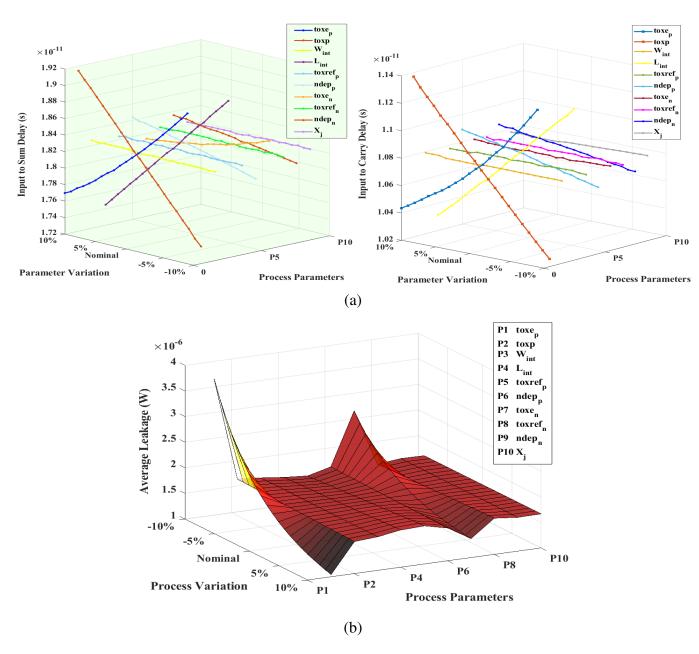

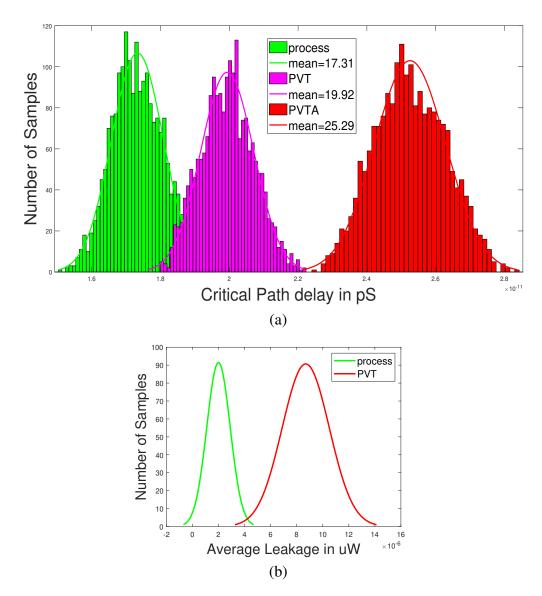

Process variations are further divided up into inter-die and intra-die variations. Intra-die variations are disparities in device features that exist within a single chip, implying that a device feature differs between different locations on the same die. Intra-chip variations frequently exhibit spatial correlations, with devices placed close to each other having a higher probability of being alike than devices placed far apart. Intra-die variations also exhibit structural correlations, which means that devices that are structurally similar have a higher likelihood of having similar device features, such as devices oriented in the same direction. Inter-chip variations are disparities that occur from one die to the next, implying that the same device on a chip has different features from one wafer to the next, wafer to wafer, and wafer lot to wafer lot. With increased process scaling, intra-chip variations are becoming a larger part of overall device feature variability, which means that devices on the same die can no longer be treated as identical copies of the same device. The impact of process parameters on Performance parameters of 1b-Full Adder circuit is represented in Fig.3.5

# 3.3 Operating Variations: Supply Voltage and Temperature

The operating variations like temperature and supply voltage cannot be neglected and have a significant impact on the performance parameters of the circuit.

# 3.3.1 Supply Voltage

From the previous sections, it is evident that power dissipated is linearly dependent on supply voltage i.e., reducing the supply voltage can reduce the total power dissipated. However, this reduction adversely affects the overall logic delays. Signal traces within an integrated circuit have capacitance, which is influenced by factors such as trace length. When the signal's state changes (from a logic 1 to a logic 0 or vice versa), the driving transistors must transfer

Figure 3.1: Impact of Process variations on (a) Critical Path Delay and (b) Average Leakage for a Full adder

current until the desired new state is reached. The lower the supply voltage available for the IC, the longer it takes to drive the signal [8], Hence, increasing the propagational delay of the IC.

#### 3.3.2 Temperature

Environmental Temperature fluctuations can cause significant variations in the device performance as it alters the die temperature. Electronic systems mounted on automobile engines, for instance, operate in a temperature range of 40°C to 100°C. Temperature variations affect the device characteristics of MOSFETs, allowing the performance of the IC to vary. Leakage power increases exponentially with fluctuations in temperature [8].

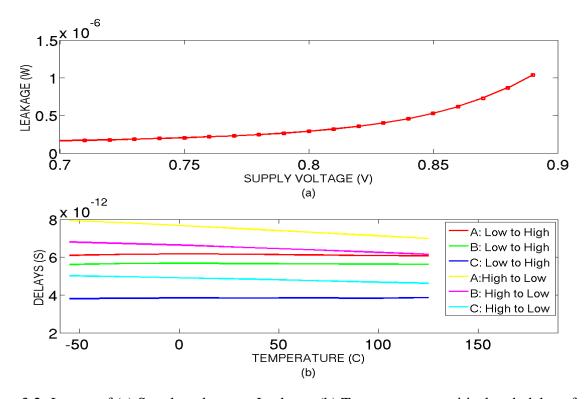

The impact of the Supply voltage and Temperature on Leakage and critical path delay is depicted in Fig.3.2

Figure 3.2: Impact of (a) Supply voltage on Leakage, (b) Temperature on critical path delay of 1b-Full Adder

#### 3.4 Aging Variations

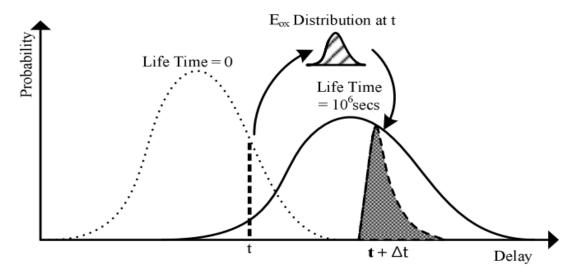

Aging variations(NBTI) change the initial performance parameters gradually over time. The charge carriers in the channel get trapped in the insulating dielectric (silicon dioxide), raising the electric field and interface traps are created over time. This process eventually builds electric charge in the dielectric, and in turn, increases the gate voltage required to turn on the MOSFET, i.e., Threshold voltage( $V_{TH}$ ). This increase in Threshold Voltage affects the switching of the transistor and makes the device slow over time as shown in Fig.3.3. Due to this increase, aging variations favor the leakage power while the delays are degraded.

This is worsened when the NBTI aging effects are severely impacted by the magnitude of process variations in parameters like oxide thickness( $T_{ox}$ ), the effective channel length ( $L_{eff}$ ), the effective channel width ( $W_{eff}$ ), and the zero-biased threshold voltage ( $V_{th0}$ ) [2].

Figure 3.3: The change of gate delay due to NBTI at D=t [2]

# 3.5 PVTA range considered for the optimization

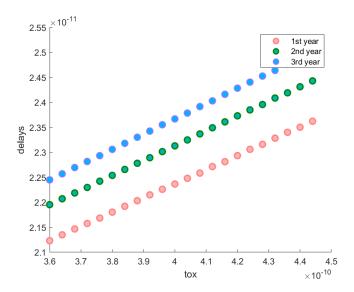

Subnanometer technology nodes have made possible highly complex ICs with superior integration of functionality. Nonetheless, migration to these regimes has increased the static power losses and rendered the circuits highly sensitive towards process parameters (P), supply voltage (V), temperature (T), and aging (A) variations. In this work, 10 significant process parameters are considered like channel-length and channel-width offset parameter (lint, wint), physical

gate equivalent oxide thickness (toxp), electrical gate equivalent oxide thickness ( $toxe_n$ ,  $toxe_p$ ), nominal gate oxide thickness for gate dielectric tunneling current ( $toxref_n$ ,  $toxref_p$ ), junction depth (xj) and channel doping concentration at depletion edge ( $ndep_n$ ,  $ndep_p$ ). The process parameters are considered at  $3\sigma$  value of  $\pm 10\%$  variation from the nominal value of the process parameters mentioned in Table 3.1.

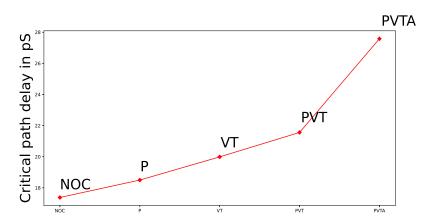

The temperature range of [-55 °C to 125 °C] has been considered for optimization, with  $\pm 10\%$  variation in supply voltage i.e. [0.72 to 0.88] and 3 years of NBTI aging. The impact of the Process, operating and Aging variations on Critical path delay and Average leakage power of 1b-FUll Adder circuit is represented in Fig.3.4 and Fig.3.5

| Sr.no | process parameter | Lower deviation | Nominal value | Higher deviation |

|-------|-------------------|-----------------|---------------|------------------|

| 1     | lint              | 1.2307e-009     | 1.35e-009     | 1.489e-009       |

| 2     | wint              | 4.4868e-009     | 5e-009        | 5.4849e-009      |

| 3     | toxp              | 3.658e-010      | 4e-010        | 4.393e-010       |

| 4     | $toxe_n$          | 5.8436e-010     | 6.5e-010      | 7.27e-010        |

| 5     | $toxe_p$          | 5.978e-010      | 6.7e-010      | 7.487e-010       |

| 6     | $toxref_n$        | 5.743e-010      | 6.5e-010      | 7.251e-010       |

| 7     | $toxref_p$        | 6.08e-010       | 6.7e-010      | 7.429e-010       |

| 8     | xj                | 6.523e-009      | 7.2e-009      | 7.845e-009       |

| 9     | $ndep_n$          | 1.05e+019       | 1.2e+019      | 1.304e+019       |

| 10    | $ndep_p$          | 3.879e+018      | 4.4e+018      | 4.869e+018       |

Table 3.1: Process variations considered for 22nm CMOS technology

Throughout this thesis, we refer to

- Nominal operating conditions (NOC) as Temp=25  $^{\circ}$ C and  $V_{dd}$ = 0.8V

- Worst case operating conditions (WCO) as Temp [-55°C 125°C] and  $V_{dd}$  = [0.72 0.88]V.

- PVT as  $\pm 3\sigma$  variation in process parameters at WCO.

- PVTA refers to PVT with 3 years of NBTI degradation.

# 3.6 Literature Survey

Several approaches have previously been proposed to optimize the primary performance parameters. Channel Engineering techniques [9] like retrograde doping and halo doping reduce

Figure 3.4: Impact of Process, Operating and Aging variations on critical path delay of Full adder at nominal sizing

the power while, other conventional techniques, for example, dual-threshold CMOS, Multithreshold CMOS, Power gating, Input Vector Control (IVC) [10], [11] reduce the power in standby and active modes. Leakage power analysis on nano-scale technologies is performed in [12] for low-power and high-performance applications.

However, transistor sizing is the most prominent technique and has many advantages which include reducing the glitches [13], balancing the load across multiple delay paths [14], parametric yield calculation [15], [16], and optimizing the performances [17] [18]. Ref [19] studied the impact of aging variations, while [20] considers the aging variations and optimizes the performances using ILP based algorithm.

Algorithm-based transistor sizing has been a salient technique to optimize the performances, but many of the previous works did not consider all the PVTA constraints in their work. [21] optimizes the CMOS circuit using the gradient-based algorithm and portrays a detailed study of the performance deviations and the extent of optimization with and without considering PVT variations. [22] focuses on the optimization of critical path delays but does not consider the PVTA constraints. [23] & [24] use NSGA-II and PSO algorithms to optimize analog circuits. Popular algorithms such as Genetic Algorithm (GA) [25], Particle swarm optimization (PSO) [26], NSGA-II and other swarm-based algorithms [27], [28] have been used in various scenarios obtaining appreciable optimizations but doesn't consider PVT variations. Genetic algorithms are time-consuming while swarm-based algorithms overcome the runtime issue [26].

Figure 3.5: Impact of Process variations on (a) Critical Path Delay and (b) Average Leakage for a Full adder

In [29] & [30], Process variations have been considered, but the aging effect is not considered, that too the process variations considered are for only the corner cases. [31] optimizes leakage only for standby mode. Moreover, in [29], [30] & [31]

# 3.7 Summary

The miniaturization of MOS devices to lower technology nodes made process variations significant in fabrication. This disparity in process parameters (e.g., tox, VT, junction depth, etc.) has become acute as it leads to an increase in leakage power as well as propagation delays. This poses a serious problem in meeting the desired timing and power criteria of the present day low power and high performance circuits. In our proposed optimization methodology, we have considered 10 significant process parameters at  $3\sigma$  variation for 22nm MGK technology.

In addition to process variations, operating variations, and aging degradation are other factors that deviate the circuit's performance (leakage power and delays). Any deviation in operating parameters like supply voltage and temperature may cause a huge variation in leakage power and propagation delays. To meet the required circuit's specifications, all such variations have to be taken into account to avoid any discrepancy in the circuit's performance.

### Chapter 4

#### **Circuit Analysis**

#### 4.1 Introduction

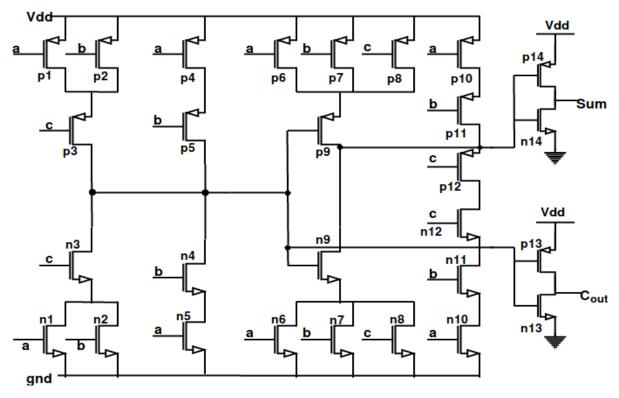

Circuit analysis is performed for a better understanding of the response of the circuit on changing various parameters like design parameters, local and global process parameters, the correlation between process parameters, etc. These results were taken into consideration to ease the optimization process and to obtain better results. We have presented our analysis for the 28 transistor mirror full adder shown below in Fig.4.1

# 4.2 Sensitivity Analysis

The term sensitivity refers to the impact of changing parameter values on system functionality. Sensitivity analysis allows you to determine which system parameters have the greatest influence and which have the least. Knowledge of sensitivity allows the designer of VLSI circuits to identify the number of variables that have a critical influence on the operation of the circuit[32].

As mentioned earlier varying widths and lengths can have a significant impact on leakages and delays. The impact of each independent design parameter on all the dependent performances is nothing but sensitivity analysis. With sensitivity analysis for each parameter i.e., the Length and Width of each transistor in a digital circuit, the significant design parameters can be focused to reduce the computational time with almost similar accuracy.

We have performed a sensitivity analysis for the 28T Full adder circuit in Fig.4.1 considering the length and width of each transistor as design parameters, hence, a total of 56 design

Figure 4.1: CMOS 28T Full Adder Cell

parameters.

The sensitivity of a parameter(p) is calculated by varying it by a small amount  $\Delta p$ , i.e., by sweeping the design parameter as shown in equation 4.1. The resulting performance difference  $\Delta f = f(p + \Delta p) - f(p)$  is used to calculate the sensitivity as  $\Delta f/\Delta p$ .

$$Sensitivity(\Delta p) = f(p + \Delta p) - f(p)/\Delta p \tag{4.1}$$

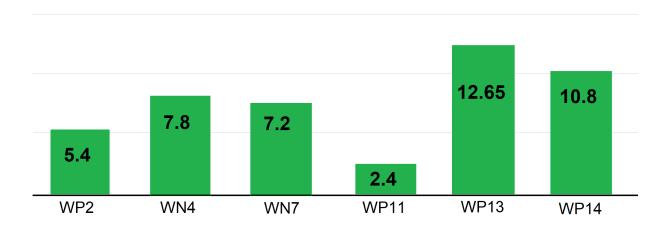

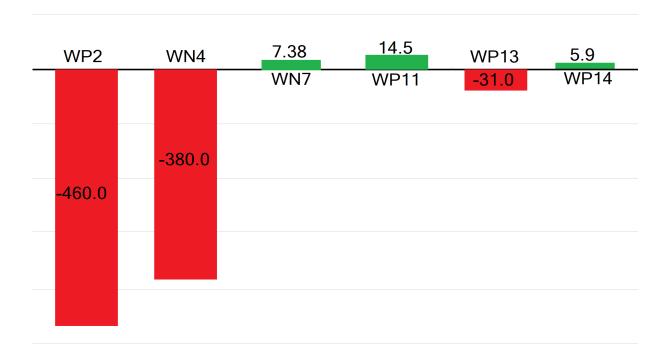

Fig(4.2a) and (4.2b) represent the sensitivity percentages of various design parameters of 28T Full adder on leakages (a) and delays (b). Table 4.1 reports the sensitivity in percentage for Widths of all the 28 transistors mentioned in Fig.4.1.

Power, area, and delay being some of the critical performance metrics, their optimization holds an integral position in the design flow. However, irrespective of the design parameters taken, their mutually contrasting feature prohibits simultaneous optimization for all three. Moreover, migration to deep sub-micron regimes enhances circuit sensitivity towards PVT variations.

# % change in Leakage from Nominal value

(a) Average Leakage

# % change in delay from Nominal value

(b) Critical Path Delays

Figure 4.2: Sensitivity of design parameters for 28T Full adder

# 4.3 Screening

Screening is the process of reducing or nullifying the effect of insignificant parameters. From the above sensitivity analysis, the parameters that have less impact are screened out, and only the parameters that have a significant impact are considered. This reduces the number of design variables and, in turn, the number of constraints in the algorithm, due to which the number of iterations and computational time drastically reduces. From the Table 4.1, the parameters that are screened out are  $W_{P10}$ ,  $W_{N11}$ ,  $W_{P11}$ ,  $W_{N12}$  and  $W_{P12}$  for low power optimization considering 5% as the maximum bound to be screened. While for High performance optimization,  $W_{N6}$ ,  $W_{P6}$ ,  $W_{N7}$ ,  $W_{P7}$ ,  $W_{N8}$ ,  $W_{P8}$ ,  $W_{N10}$ ,  $W_{P10}$ ,  $W_{N11}$ ,  $W_{P11}$ ,  $W_{N12}$ ,  $W_{P12}$ ,  $W_{N14}$  and  $W_{P14}$  are screened out. We have noticed a 64% reduction in computational time without any effect on optimization.

### 4.4 Mismatch Analysis

Mismatch analysis is the investigation of the effect of intra-die process variations on the circuit's performance parameters. A mismatch can be thought of as spatial noise spread across the surface of a chip. The main effects of mismatch on system performance are reduced dynamic range due to increased spatial noise, precision limitation, increased area, and increased power dissipation. When designing circuits, all of these constraints must be traded off against each other.

Mismatch in CMOS circuits is induced by three primary factors. The first is the variation in physical device dimensions. The only way to minimize this effect is to use large devices that can neglect the effect of variation, which often occurs at the edges of the device. The metallurgical variation of device parameters, which primarily includes the variation of doping densities in the semiconductor, is yet another source of mismatch. Using large-size transistors can also help to reduce this type of mismatch. The device's electronic parameters are the third source of mismatch. For example, trapped charges in the gate oxide or surface states in a MOS transistor can alter the device's threshold voltage. Among these, the third is discovered to be more prevalent in MOS transistors.

Mismatch analysis can be performed by applying constant inputs to the circuit and assuming mismatch levels for each transistor's threshold voltage. We have taken into account two corners of the threshold voltage with  $\pm 5\%$  variation from the nominal. We concluded from this analysis that the mismatch effect on delay and leakage is insignificant and thus negligible.

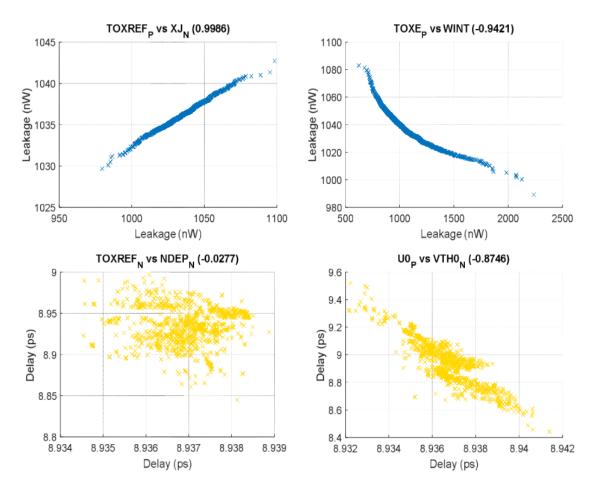

#### 4.5 Correlation

Variations in process parameters result in the variation of performance parameters to a great extent. Since the process parameters are also inter-dependent, the correlation between process parameters has to be considered before optimizing the circuit. Pearson Correlation Coefficient( $\rho$ ) between any two variables is measured as:

$$\rho = \frac{n(\Sigma xy) - (\Sigma x)(\Sigma y)}{\sqrt{[n\Sigma x^2 - (\Sigma x)^2][n\Sigma y^2 - (\Sigma y)^2]}}$$

(4.2)

Where n is the number of samples, x and y are performance parameters. The correlation percentage( $\rho * 100$ ) for a few combinations of process parameters is shown in Fig(4.4)

According to [33], BTI and process parameters are inter-dependent. Since we have considered NBTI aging effects, the correlation between NBTI and process parameters is also taken into account. Fig(4.3) shows the scatter plot for NBTI and toxp.

Figure 4.3: Correlation of aging and toxp

Figure 4.4: Correlation between few Process Parameters

| S.no | Design parameter(Width) | Sensitivity for Leakage | <b>Sensitivity for Delay</b> |

|------|-------------------------|-------------------------|------------------------------|

| 1    | $W_{p1}$                | 5.4%                    | -457%                        |

| 2    | $W_{n1}$                | 7.2%                    | -100%                        |

| 3    | $W_{p2}$                | 5.4%                    | -413.8%                      |

| 4    | $W_{n2}$                | 7.2%                    | -73%                         |

| 5    | $W_{p3}$                | 6.6%                    | -349%                        |

| 6    | $W_{n3}$                | 8.4%                    | -75%                         |

| 7    | $W_{p4}$                | 5.4%                    | -467%                        |

| 8    | $W_{n4}$                | 7.8%                    | -69%                         |

| 9    | $W_{p5}$                | 5.4%                    | -380%                        |

| 10   | $W_{n5}$                | 7.2%                    | 114%                         |

| 11   | $W_{p6}$                | 5.4%                    | -0.05022%                    |

| 12   | $W_{n6}$                | 7.2%                    | 0.0177%                      |

| 13   | $W_{p7}$                | 5.4%                    | 0.0727%                      |

| 14   | $W_{n7}$                | 7.2%                    | 0.094%                       |

| 15   | $W_{p8}$                | 5.4%                    | -0.016%                      |

| 16   | $W_{n8}$                | 7.2%                    | 0.0083%                      |

| 17   | $W_{p9}$                | 8.4%                    | 14.5%                        |

| 18   | $W_{n9}$                | 9.6%                    | 7.38%                        |

| 19   | $W_{p10}$               | 3.6%                    | 0.054%                       |

| 20   | $W_{n10}$               | 6.02%                   | -0.06519%                    |

| 21   | $W_{p11}$               | 2.4%                    | -0.0366%                     |

| 22   | $W_{n11}$               | 3.6%                    | -0.085%                      |

| 23   | $W_{p12}$               | 3.01%                   | -0.269%                      |

| 24   | $W_{n12}$               | 4.8%                    | -0.0759%                     |

| 25   | $W_{p13}$               | 10.81%                  | 5.9%                         |

| 26   | $W_{n13}$               | 12.65%                  | -31%                         |

| 27   | $W_{p14}$               | 10.81%                  | -0.09%                       |

| 28   | $W_{n14}$               | 12.65%                  | 0.19%                        |

Table 4.1: Process variations considered for 22nm CMOS technology

24

# Chapter 5

# Proposed Algorithm methodology using Transistor sizing to optimize performances of CMOS digital circuits

## 5.1 Introduction

Considering all PVTA constraints, optimizing leakage power and delay becomes the bottleneck for the designers. Varying the design parameters (Widths and Lengths) is an effective way

to optimize delays and leakages. However, with the increasing complexity of the circuits, it is

almost impossible for a human to manually change the design parameters. Therefore, we have

proposed an algorithm-based optimization scheme to find the optimal width and length values

that are robust against all PVTA variations. Fig. 5.1 clearly shows that the delays and leakage may have similar/contrary dependence on the dimensions of an individual MOS device,

providing the design space to find the optimal sizing of all MOS devices at which the CUT is

robust against all variations and working for the intended lifetime.

# 5.2 Pareto Harris Hawk optimization algorithm

Harris hawks optimization is a single objective, population based algorithm. This algorithm is inspired by the exploration methods and pouncing strategies of harris hawks. From the basic algorithm proposed in [34], we introduce a variable c to convert our two objectives leakage and delays into a single objective function (f) as

$$f = c * max(delays) + (1 - c) * average(leakages)$$

(5.1)

In eq(5.1) c=1 optimizes delays ignoring leakages and c=0 optimizes leakages ignoring delays. values of c between 0 and 1 give other points. We take the logarithm of objective

Figure 5.1: Change in delay/leakage values Vs. MOS dimensions

function as the values of the objectives are very small. Leakages are in the order of  $10^{-6}$  while delays are in the range of  $10^{-12}$ . Taking a logarithm normalizes these values. Due to this, the linear combination tends to increase weightage for one objective creating bias. Hence we use exponentially varying weightage values to get even distribution of points to counter this effect. That is, instead of C varying as 0.1, 0.2, 0.3,... incrementation is done by eq(5.2). The value of k changes from 3-6 to get various points of optimality.

$$c_i = 1 - 1/k^i (5.2)$$

This algorithm has 3 main phases. Exploration phase, Transition phase and Exploitation Phase. In Exploration Phase, they search for the Prey based on probability q. Each Hawk is a solution and the best Hawk in step is the solution of that step. Their behavior is modeled by eq(5.3) where X(t+1) is the position in the next iteration,  $H = (LB + r_4(UB - LB))$  and  $r_1$ ,  $r_2$ ,  $r_3$  and  $r_4$  are random numbers inside (0,1).

$$X(t+1) = \begin{cases} X_{rand}(t) - r_1 |X_{rand}(t) - 2r_2 X(t)|, & \text{if } q \ge 0.5\\ (X_{prey}(t) - X_m(t)) - r_3 H), & \text{if } q < 0.5 \end{cases}$$

(5.3)

Energy of Harris hawks(E) is calculated as  $E = 2E_0(1 - \frac{t}{T})$ , where  $E_o$  changes randomly in interval (-1,1). Hence, Harris Hawks search for the Prey if  $|E| \ge 1$  and when |E| < 1 they go to Exploitation phase.

In the Exploitation Phase, Harris Hawks perform surprise pounce. This phase has 4 cases based on the escaping probability of the prey r ( $r \ge 0.5$ , the prey escapes) and the Escaping energy E.

#### **5.2.1** Case1:

When  $r \ge 0.5$  and  $|E| \ge 0.5$ , the behaviour of Harris Hawks is modeled as shown below in eq(5.4), Where  $J = 2(1 - r_5)$  and is a random number between 0 and 1.

$$X(t+1) = \Delta X(t) - E|JX_{prey}(t) - X(t)|$$

$$\Delta X(t) = X_{prey}(t) - X(t)$$

(5.4)

#### 5.2.2 Case2:

When  $r \ge 0.5$  and |E| < 0.5, the prey is exhausted and has low Energy. Harris Hawks hardly encircle the prey and perform surprise pounce. This is modeled below by eq(5.5).

$$X(t+1) = X_{prey}(t) - E|\Delta X(t)| \tag{5.5}$$

#### 5.2.3 Case3:

When r<0.5 and  $|E| \ge 0.5$ , they prey will have enough energy to escape and Harris Hawks perform rapid dives to correct their location with respect to the deceptive location of the prey. This is called Levy Flight(LF) and is modelled by the eq(5.6). Where D is the dimension and S is vector of Dimension 1xD, below mentioned u and v are random values between 0 and 1,  $\beta$  is set to 1.5

$$Y = X_{prey}(t) - E|\Delta X(t)|$$

$$Z = Y + S * LF(D)$$

$$LF(x) = 0.01(\frac{u\sigma}{|v|^{\frac{1}{\beta}}})$$

$$\sigma = (\frac{\gamma(1+\beta)x\sin(\frac{\pi\beta}{2})}{\gamma(\frac{1+\beta}{2})\beta2^{\frac{\beta-1}{2}}})^{\frac{1}{\beta}}$$

$$X(t+1) = \begin{cases} Y & \text{if } F(Y) < F(X(t)) \\ Z & \text{if } F(Z) < F(X(t)) \end{cases}$$

$$(5.6)$$

### 5.2.4 Case4:

r<0.5 and |E| <0.5, in this case the prey has low energy and the Harris Hawks hardly encircle the prey. They attack and kill the prey. This is modelled as below: eq(5.7), where  $X_m(t)$  is the average of positions of hawks.

$$Y = X_{prey}(t) - E|X_{prey} - X_m(t)|$$

$$X(t+1) = \begin{cases} Y & \text{if } F(Y) < F(X(t)) \\ Z & \text{if } F(Z) < F(X(t)) \end{cases}$$

(5.7)

#### Algorithm 1: Pareto Harris Hawks optimization Algorithm

```

1 Set Number of iterations(i) and Population Size (N);

2 Initialize Random Population;

3 for number of iters i do

Calculate fitness of Hawks using Eq.5.1;

4

Set X_{prey} as the best solution;

5

for each hawk do

6

Update E;

7

if |E| \geq 1: Exploration Phase then

8

Use Eq.5.3;

9

10

else

11

Exploitation phase;

12

if r \ge 0.5 |E| \ge 0.5 : Case1 then

13

Use Eq.5.4;

14

else if r > 0.5|E| < 0.5 : Case2 then

16

Use Eq.5.5;

17

else if r < 0.5|E| \ge 0.5 : Case3 then

18

Use Eq.5.6;

19

else

20

Use Eq.5.7;

21

Update X_{prey} with the location of Hawk with best fitness;

22

```

# 5.3 Neighbourhood Cultivation Genetic Algorithm

Neighbourhood Cultivation Genetic Algorithm (NCGA) [35] is an extension of the Genetic algorithm. This includes the mechanisms of NSGA-II [36] and SPEA-II [37] as well as the neighbourhood crossover mechanism. If the distance between two parents is more, then the crossover may have no effect on local search. Unlike the crossover in other algorithms like GA, NSGA-II and SPEA-II, NCGA selects the neighbours for crossover instead of randomly chosen individuals. Thus the resulting child individuals have more traits like their parents. This algorithm is initialized with a random population of size N, and then they are sorted according to the focused objective. The objective changes in each iteration. If there are 8 objectives to be

optimized, the first objective is chosen in the first iteration, the second objective in the second iteration and eighth objective in the eighth iteration and the first objective again in the ninth iteration and so on. From the sorted individuals, the neighbouring individuals are grouped for crossover and mutation. Crossover and mutation are similar to that in SPEA-II. The required objectives are calculated for the child individuals, and the new population of size N is chosen from the child individuals of size N and the current population of size N by environmental selection. These steps are repeated for the new population until the termination criterion is met.

### Algorithm 2: Neighbourhood Cultivation Genetic Algorithm

- 1 Set Number of iterations(i) and Population Size (N);

- 2 Initialize the Population for number of iters i do

- **for** each individual **do**

- 4 obtain focused obj as per the iteration;

- 5 Sort the Individuals based on the focused objective;

- 6 Group the Individuals with their neighbours;

- Generate the Individuals with crossover and mutation;

- 8 Eval the focused objective;

- 9 Replace the worst individuals with the best ones;

# 5.4 Strength Pareto evolutionary algorithm - II (SPEA-II)

SPEA-II [37] is a multi-objective optimization algorithm that is an extension of the SPEA algorithm proposed in [38]. This algorithm incorporates a fine-grained fitness assignment strategy, a density estimation technique, and an enhanced archive truncation method compared to the previous SPEA algorithm. Initial population  $P_0$  of size N and Archive  $A_0$  of size N' are initialized. In each iteration, the fitness of each individual F(i) is calculated as F(i) = D(i) + R(i) where D(i) is the density and R(i) is the raw fitness and are calculated by eq. (5.8) (5.9) and (5.10).

$$S(i) = |\{j|j \in P_t + \overline{P_t} \wedge i\phi j\}|$$

(5.8)

$$R(i) = \sum_{j \in P_t + \overline{P_t}, j \neq i} S(j)$$

$$(5.9)$$

$$D(i) = \frac{1}{\sigma_i^k + 2} \tag{5.10}$$

Each individual i in the archive  $\overline{P_t}$  and the population  $P_t$  is assigned a strength value S(i) of eq. (5.8), representing the number of solutions it dominates, where  $\phi$  corresponds to the Pareto dominance relation. On the basis of the S values, the raw fitness of individual R(i) is calculated as eq.(5.9). Density D(i) of individual i is calculated as eq.(5.10), where  $\sigma_i^k$  is the  $k^{th}$  element for each individual i the distances to all individuals in archive and population after sorting the list in increasing order. The non-dominated individuals based on fitness from  $P_t$  and  $A_t$  are moved to  $A_{t+1}$ . If the size of  $A_{t+1}$  is less than N',  $A_{t+1}$  is filled with few of the dominated individuals from  $P_t$  and  $A_t$ . Whereas, If the size of  $A_{t+1}$  exceeds N', some individuals are removed from  $A_{t+1}$  using the truncation operator. Crossover and mutation, similar to that in SPEA [38], are performed. These steps are repeated until the termination criterion is met. In this algorithm each individual of the population corresponds to one set of sizing and the dimension of each individual is the total number of Widths and Lengths in the circuit. The focused objective is average leakage for low power applications and Critical path delay for high performance applications.

Algorithm 3: SPEA-II: Improving Strength Pareto Evolutionary Algorithm

```

1 Set Number of iterations(t);

2 Initialize the Population(P_0) of size N and create Archive(A_0) of size N';

3 for number of iters t do

for each individual i do

4

Compute Fitness F(i) of individual i of P_t and A_t as in eq.(5.10);

5

Add non-dominated individuals from P_t and A_t to A_{t+1};

6

if size of A_{t+1} is less than N' then

7

Add dominated individuals from P_t and A_t to A_{t+1};

8

9

else if size of A_{t+1} exceeds N' then

10

Remove individuals from A_{t+1} using Truncation Operator;

11

Perform binary selection to create mating pool;

12

Generate the Individuals with crossover and mutation;

13

Evaluate the focused objective;

14

```

# 5.5 Glowworm swarm optimization algorithm

Glowworm swarm optimization (GSO) [39] imitates the behaviour of glowworms. This algorithm has four main phases: Initialization, Updating luciferin value, movement and updating local decision range. In the Initialization phase, each glow worm is arbitrarily assigned to an

initial position in the feasible domain and has a random local decision range. The higher the luciferin value, more brighter the glow worm is and hence better the position of the glow worm. Brighter glow worms have a low radius for local decision range and vice versa. The brighter glow worms attract the glow worms in the local decision range. They choose different neighbours every time based on brightness. Hence the direction of movement keeps changing. Then the luciferin value is computed at the new position. The glow worms update their luciferin value based on their position using eq(5.11)

$$l_i(t) = (1 - \rho)l_i(t - 1) + \gamma J(x_i(t))$$

(5.11)

Based on the Luciferin value the brighter glow worms attract other glow worms in their local decision range. They move in the direction of high Probability. The Probability and direction j are calculated using the below equations eq(5.12) & eq(5.13).

$$P_{ij} = \frac{l_j(t) - l_i(t)}{\sum_{k \in Neighbourhood} l_k(t) - l_i(t)}$$

(5.12)

$$j =_i P_{ii} \tag{5.13}$$

They update the local decision range after going to their position. If the Luciferin Value is high, they have a low radius for the local decision range and vice versa, it is also updated in this phase using the below equations. where, in eq(5.14),  $X_i$  is the position of i<sup>th</sup> glow worm and in equation eq(5.15),  $r_i^d$  is the local decision range and  $N_i$  is the neighbourhood

$$X_i(t+1) = X_i(t) + s \frac{X_j(t) - X_i(t)}{\|X_j(t) - X_i(t)\|}$$

(5.14)

$$r_i^d = \min(r_s, \max(0, r_i^d(t), \beta(n_t - N_i(t))))$$

(5.15)

#### **Algorithm 4**: Glow Worm Swarm Optimization

- 1 Set the number of iters and bounds on the position of glowworms;

- 2 Initialize the number of glow and their positions: stage-1;

- 3 Calculate the Luciferin value based on the Position of each glowworm;

- 4 for number of iters do

```

for each worm: stage 2 do

5

Update luciferin value based on the position of glowworm;

6

for each worm: stage 3 do

7

Search for the brightest;

8

Calculate the probability of movement in all directions and select the best using

5.12 & 5.13;

Update the new location using 5.14

10

for each worm: stage 4 do

11

Update the local decision range using 5.15

12

```

13 Compute coordinates with better luciferin value

## 5.6 Implementation

All the optimization algorithms mentioned above have been developed and tested over several basic standard cells to optimize critical path delay keeping leakage power in bound (for high-performance applications) and vice versa i.e. optimizing leakage power with critical path delay in bound (for low-power applications) with the confidence, the optimized circuit will be robust against all process variations, fully functional for the targeted temperature range and supply voltage and work for the intended year. To perform PVT and aging degradation aware circuit sizing and optimization, the essential requirement is a transistor level net-list supporting both fresh as well as degraded over year device operation. The proposed work uses the MOS Reliability Analysis (MOSRA) tool for pre and post stress simulation integrated within the HSPICE simulator [40][41]. The present optimization results are limited to 22nm CMOS technology node. However, the proposed methodology is equally valid for other technology nodes.

The optimization scheme is a highly simulation intensive task. Therefore, it is always good to first optimize the CUT at nominal operating conditions (Temp= $25^{\circ}$ C,  $V_{dd}$ = 0.8V) i.e. first find the circuit safety margin which ultimately improves computational efforts when all PVTA variations are included.

After the initial part of the analysis, bounds are set on design parameters and performance parameters. In the circuit sizing and optimization of circuits, the design parameters mainly consist of channel lengths(L) and widths(W) of all devices. Such design parameters are tuned, within the bounds mentioned in Table. (5.1)

| Design Parameter | Lower Bound | Initial Value (Min) | Upper Bound |

|------------------|-------------|---------------------|-------------|

| L_PMOS           | 22nm        | 22nm                | 25nm        |

| L_NMOS           | 22nm        | 22nm                | 25nm        |

| W_PMOS           | 44nm        | 88nm [15]           | 800nm       |

| W_NMOS           | 44nm        | 88nm [15]           | 800nm       |

Table 5.1: Initial sizing and bounds of the design Parameters

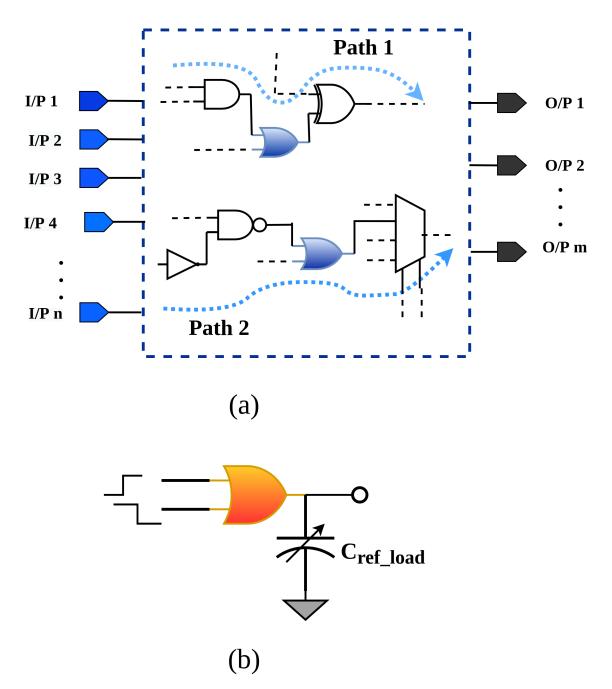

In the circuit sizing and optimization of circuits, the design parameters mainly consist of channel lengths(L) and widths(W) of all devices. Such design parameters are tuned, within specified bound (shown in Table. 5.1) during the optimization phase to fulfill the performance specifications incorporating all PVTA variations. We have also ensured the indigenous working of the final optimized circuit through the entire range of process parameters, aging variations and operating variations. An overview of the optimization process is shown in Fig.(5.2)

We presented detailed optimization results for a 1-bit CMOS mirror Full Adder(FA) circuit consisting of 28 transistors and thus 56 design parameters. The initial sizing of all MOS devices in FA are taken from [42] and the optimized results for high performance applications, i.e., critical path delays are well below the delays of initially sized FA at NOC are reported in Table. 5.2. Also reported for optimization results at NOC. The final robust sizings of all the MOS devices in FA for high performance applications are reported in Table.5.3.

Table 5.4 and Table 5.5 report results for high performance and low power applications of basic cells respectively. Fig.(5.3) shows the optimization of various basic cells for high performance applications. It is to be noted that the algorithms are modified according to the initial analysis performed. This includes determination of variable value bounds, selection of significant design variables to be modified and the range of process and operating parameters to be used to test the robustness of the design.

| Performances         | Initial |       | G     | SO    | NCGA  |       | SPEA2 |        | ННО   |        |

|----------------------|---------|-------|-------|-------|-------|-------|-------|--------|-------|--------|

| 1 CHOITHAILCES       | NOC     | PVTA  | NOC   | PVTA  | NOC   | PVTA  | NOC   | PVTA   | NOC   | PVTA   |

| AvgLeak (µW)         | 1.66    | 6.22  | 1.61  | 6.105 | 1.63  | 6.19  | 1.61  | 6.02   | 1.64  | 6.20   |

| $T_{plh\_a\_C}$ (ps) | 8.21    | 10.96 | 9.18  | 13.68 | 11.87 | 16.67 | 11.40 | 16.15  | 8.71  | 13.76  |

| $T_{phl\_a\_C}$ (ps) | 10.01   | 16.10 | 8.24  | 13.88 | 9.46  | 15.49 | 8.66  | 14.31  | 9.63  | 13.26  |

| $T_{plh\_b\_C}$ (ps) | 7.05    | 9.69  | 9.77  | 14.53 | 9.05  | 13.64 | 10.10 | 14.83  | 9.28  | 15.23  |

| $T_{phl\_b\_C}$ (ps) | 9.97    | 15.36 | 9.23  | 14.27 | 10.29 | 16.03 | 9.20  | 14.49  | 9.08  | 13.65  |

| $T_{plh\_c\_C}$ (ps) | 8.15    | 10.45 | 10.40 | 14.38 | 10.12 | 9.92  | 13.67 | 6.105  | 8.62  | 15.32  |

| $T_{phl\_c\_C}$ (ps) | 9.42    | 14.17 | 8.58  | 13.58 | 10.44 | 16.76 | 7.37  | 11.69  | 8.71  | 13.29  |

| $T_{plh\_a\_S}$ (ps) | 15.45   | 20.8  | 9.54  | 13.71 | 12.23 | 16.44 | 11.49 | 15.478 | 10.37 | 13.96  |

| $T_{phl\_a\_S}$ (ps) | 17.38   | 27.58 | 9.08  | 15.60 | 10.00 | 16.67 | 9.57  | 16.15  | 9.38  | 15.08  |

| $T_{plh\_b\_S}$ (ps) | 14.93   | 21.19 | 9.65  | 13.82 | 9.01  | 13.04 | 11.25 | 15.92  | 10.66 | 14.78  |

| $T_{phl\_b\_S}$ (ps) | 15.14   | 24.01 | 9.71  | 15.48 | 10.21 | 16.43 | 9.97  | 16.18  | 10.52 | 15.296 |

| $T_{plh\_c\_S}$ (ps) | 15.03   | 20.07 | 10.33 | 13.60 | 11.68 | 15.67 | 11.04 | 14.70  | 10.44 | 13.98  |

| $T_{phl\_c\_S}$ (ps) | 15.62   | 23.26 | 9.00  | 14.49 | 10.02 | 16.34 | 8.46  | 13.70  | 9.18  | 15.295 |

Table 5.2: PVTA invariant optimization results for CMOS 28T 1-bit Full Adder (for high-performance circuits)

Figure 5.2: Overview of basic cell optimization

| Sizings     | Initial | GSO    | NCGA   | SPEA-II | ННО    |

|-------------|---------|--------|--------|---------|--------|

| p1          | 352/22  | 376/22 | 623/22 | 398/22  | 565/22 |

| n1          | 176/22  | 545/22 | 346/22 | 608/22  | 185/22 |

| p2          | 352/22  | 259/22 | 343/22 | 497/22  | 313/22 |

| n2          | 176/22  | 361/22 | 182/22 | 196/22  | 147/22 |

| p3          | 352/22  | 485/22 | 262/22 | 436/22  | 344/22 |

| n3          | 176/22  | 152/22 | 152/22 | 150/22  | 155/22 |

| p4          | 352/22  | 498/22 | 446/22 | 380/22  | 369/22 |

| n4          | 176/22  | 171/22 | 126/22 | 111/22  | 175/22 |

| p5          | 352/22  | 308/22 | 229/22 | 352/22  | 341/22 |

| n5          | 176/22  | 176/22 | 576/22 | 329/22  | 366/22 |

| <i>p</i> 6  | 352/22  | 900/23 | 563/22 | 451/22  | 630/24 |

| n6          | 176/22  | 671/23 | 551/22 | 265/23  | 730/22 |

| p7          | 352/22  | 236/22 | 377/22 | 352/23  | 900/23 |

| n7          | 176/22  | 239/22 | 370/22 | 531/22  | 880/23 |

| p8          | 352/22  | 333/22 | 235/22 | 799/25  | 227/23 |

| n8          | 176/22  | 609/22 | 722/22 | 555/22  | 900/22 |

| p9          | 352/22  | 236/22 | 377/22 | 352/23  | 900/23 |

| n9          | 176/22  | 239/22 | 370/22 | 531/22  | 880/23 |

| p10         | 528/22  | 145/22 | 427/22 | 897/22  | 98/23  |

| n10         | 264/22  | 529/22 | 776/22 | 407/22  | 314/23 |

| <i>p</i> 11 | 528/22  | 44/22  | 44/23  | 65/22   | 112/22 |

| n11         | 264/22  | 329/22 | 44/24  | 165/22  | 44/22  |

| <i>p</i> 12 | 528/22  | 44/23  | 44/22  | 44/22   | 44/23  |

| n12         | 264/22  | 22/24  | 44/22  | 44/23   | 44/23  |

| p13         | 352/22  | 44/22  | 44/22  | 44/22   | 44/22  |

| n13         | 176/22  | 55/23  | 44/22  | 44/22   | 44/22  |

| p14         | 352/22  | 265/22 | 198/22 | 379/22  | 253/22 |

| n14         | 176/22  | 87/22  | 79/22  | 188/22  | 220/22 |

Table 5.3: Robust Sizing obtained for  $28\mathbf{T}$  1-bit Full Adder cell at  $22\mathrm{nm}$  technology node

37

| Circ    | Circuit |       | ННО    | NCGA  | GSO   | SPEA-II |

|---------|---------|-------|--------|-------|-------|---------|

| AND3    | PVTA    | 13.24 | 8.62   | 8.51  | 8.97  | 9.53    |

| ANDS    | NOC     | 9.24  | 5.4    | 5.37  | 5.63  | 6.18    |

| NAND3   | PVTA    | 10.81 | 6.7    | 6.9   | 6.7   | 7.13    |

| INAINDS | NOC     | 7.05  | 4.6    | 5.1   | 4.9   | 5.05    |

| NOR3    | PVTA    | 11.37 | 6.8    | 7.4   | 7.1   | 7.82    |

| NC NC   | NOC     | 7.56  | 6.98   | 5.6   | 5.02  | 5.21    |

| MUX     | PVTA    | 10.78 | 7.2    | 7.5   | 7.33  | 8.03    |

| WIOX    | NOC     | 7.86  | 5.5    | 5.8   | 5.4   | 5.8     |

| XOR2    | PVTA    | 8.39  | 5.8    | 6.1   | 6.01  | 6.7     |

| AORZ    | NOC     | 6.11  | 4.7    | 4.9   | 4.6   | 4.9     |

| FA      | PVTA    | 27.58 | 15.296 | 16.76 | 15.6  | 16.18   |

| 1'A     | NOC     | 17.58 | 10.66  | 12.23 | 10.40 | 11.49   |

$\begin{array}{c} \text{Table 5.4: Critical path delay}(ps) \text{ optimization of Basic cells at 22} nm \text{ technology at NOC} \\ \text{and PVTA conditions} \end{array}$

| Circ  | uit | Initial | ННО   | NCGA  | GSO   | SPEA-II |

|-------|-----|---------|-------|-------|-------|---------|

| AND3  | PVT | 2.769   | 1.32  | 1.54  | 1.41  | 1.402   |

| AND3  | NOC | 0.312   | 0.144 | 0.151 | 0.148 | 0.167   |

| NAND3 | PVT | 2.022   | 1.16  | 1.32  | 1.24  | 1.28    |

| NANDS | NOC | 0.217   | 0.11  | 0.15  | 0.13  | 0.129   |

| NOR3  | PVT | 1.216   | 0.68  | 0.73  | 0.71  | 0.72    |

| NOR3  | NOC | 0.282   | 0.15  | 0.18  | 0.17  | 0.14    |

| MUX   | PVT | 3.1     | 1.31  | 1.47  | 1.33  | 1.26    |

| MUA   | NOC | 0.92    | 0.41  | 0.58  | 0.45  | 0.42    |

| XOR2  | PVT | 7.487   | 3.46  | 3.94  | 3.81  | 3.975   |

| AUKZ  | NOC | 0.586   | 0.33  | 0.42  | 0.39  | 0.28    |

| FA    | PVT | 15.83   | 5.83  | 6.28  | 6.12  | 5.91    |

| IA    | NOC | 1.72    | 0.59  | 0.61  | 0.65  | 0.72    |

Table 5.5: Average Leakage ( $\mu W$ ) optimization of Basic cells at 22nm technology for NOC and PVT conditions

Figure 5.3: Delay optimization with PVTA variations for Basic cells

# Chapter 6

# Top level framework for Complex circuit optimization

## 6.1 Introduction